# University of South Florida

# **DIGITAL COMMONS** @ UNIVERSITY OF SOUTH FLORIDA

# Digital Commons @ University of South Florida

USF Tampa Graduate Theses and Dissertations

**USF Graduate Theses and Dissertations**

10-21-2014

# **Auxiliary Roles in STT-MRAM Memory**

Jayita Das University of South Florida, jayita.365@gmail.com

Follow this and additional works at: https://digitalcommons.usf.edu/etd

Part of the Electrical and Computer Engineering Commons

#### **Scholar Commons Citation**

Das, Jayita, "Auxiliary Roles in STT-MRAM Memory" (2014). USF Tampa Graduate Theses and Dissertations.

https://digitalcommons.usf.edu/etd/5613

This Dissertation is brought to you for free and open access by the USF Graduate Theses and Dissertations at Digital Commons @ University of South Florida. It has been accepted for inclusion in USF Tampa Graduate Theses and Dissertations by an authorized administrator of Digital Commons @ University of South Florida. For more information, please contact digitalcommons@usf.edu.

# Auxiliary Roles in STT-MRAM Memory

by

Jayita Das

A dissertation submitted in partial fulfillment of the requirements for the degree of Doctor of Philosophy Department of Electrical Engineering College of Engineering University of South Florida

Co-Major Professor: Sanjukta Bhanja, Ph.D. Co-Major Professor: Syed M. Alam, Ph.D. Gokhan Mumcu, Ph.D. Selcuk Kose, Ph.D. Sudeep Sarkar, Ph.D.

> Date of Approval: October 21, 2014

Keywords: Logic-in-Memory, MTJ, Authentication, STT Clocking, Coupling

Copyright © 2014, Jayita Das

# **DEDICATION**

To my parents and sister.

### ACKNOWLEDGMENTS

A journey of close to four years is nearing its end. I would acknowledge it has been one of the most fulfilling years of my life where failures met successes, rejects met accepts and learning met obstacles. Along its way I have met various individuals who have uniquely contributed with their meticulous hands to shape it the way it is today. The first person is my advisor Dr. Sanjukta Bhanja. Our first telephonic conversation goes back to winter of 2009 when I had requested information for a graduate student position. I got a fresh opportunity to restart my career and fulfill my dreams. Her increased belief in me increased my confidence. She went on to nominate me for the Presidential Doctoral Fellowship, the highest fellowship awarded by the university. Here I would also like to thank Dr. Morgera for the nomination. In these years Dr. Bhanja gave me the freedom to explore, gave me the scope to imagine endlessly and appreciated all my creative efforts. With time she continued to assign me with greater responsibilities to grow in the role of a technical leader and engaging me in activities beyond research. She encouraged me to attend conferences and involve in outreach. Her patience has been remarkable when I failed and her feedback has been critical to my improvement. I would say that she has been one of my best critics in these years. Ending without acknowledging some of our open discussions and arguments in topics beyond research will only result in not acknowledging one vital skill that I acquired, the skill to persuasively and fearlessly defend my thoughts as a Ph.D. student.

My first association with my co-advisor Dr. Syed M. Alam dates back to the time when I was still in India. He shared materials so that I could start early on my research. His feedback and encouragement has been instrumental in my pursuits for the unknown. I would like to

thank him for the countless hours that he tirelessly devoted on me as I stumbled on problems to arrive at solutions. There is no counting of the hours that he spent correcting my writing as I struggled initially. I thank him for his patience, his encouragement, his appreciations and his guidance. He has been one of my inspirations for hard work, integrity, precision and determination.

Dr. Mumcu has been the professor known in our department to challenge his students. My first association with him was in his RF class of Fall 2011. The class was both thrilling and fun-filled, wrapped with challenges and stricter deadlines at the end of every week. The ardent desire to beat those challenges and kept alive by his constant encouragement has on multiple accounts brought the best out of me, the surprising potentials within me. This desire was further fueled by his positive criticisms, his belief in me, his offering of tougher challenges, his embedding within me a never give up attitude and his devoting selfless hours to debugging our homework problems whenever we showed up at his door. Needless to mention I went on to take all of his courses in the next two years ending each of them with greater and greater self-confidence. Dr. Mumcu has been one of my pillars of inspiration.

It was in the Spring of 2011 that I enrolled in Dr. Sarkar's class of probability estimation modeling and inference. The learning curve in class was steep, almost vertical and the experience everlasting. The assignments were equally challenging. I remember him as the awe-inspiring professor who did all the mind-blowing intricate derivations by hand in class and had all the admirations I could have for a professor at that time. He has since then been one of my role models for dedication, precision and integrity. I thank him for the example he set to us and his support on numerous occasions later in my life.

I would also like to thank my committee member Dr. Kose for readily willing to be in my committee and encouraging me from time to time whenever we met.

In these four years the contribution of my friends has been no less significant. I got all the support that I could ask for in these years from Abhishek, Yasaswini, Deepti, Rasika, Ravi, Ravikiran, Piyali, Miriam and Vaishnavi. They rejoiced in my successes and stood by my failures. This is also the time to thank Nalini who sheltered me in Washington at a time when I needed it the most. Thanks to Sagarika for doing the same in Florida when I faced unprecedented events. Here comes the time to thank Alex, Ben and his family for making sure that I didn't confine my Christmases to my study table. I would also like to thank Mr. Batson for his support, encouragement, motivation and help and the Graduate school for the fellowship that made all of this possible. My special thanks are for Kimberly Carter for her instant help regarding my travels, registrations and so much more. It is also the time to thank my department and all its staff for their support in diverse ways. Finally, I would like to thank my lab members for all the fun-filled days, the discussions and their encouragement. My achievements and this dissertation remains incomplete without acknowledging the unconditional love and support that I got from my parents and sister. Without them the story would have had a different ending....

# TABLE OF CONTENTS

| LIST OF TABLES                                        | iv  |

|-------------------------------------------------------|-----|

| LIST OF FIGURES                                       | V   |

| ABSTRACT                                              | vii |

| CHAPTER 1 INTRODUCTION                                | 1   |

| 1.1 Background                                        | 1   |

| 1.2 Motivation                                        | 3   |

| 1.3 Contribution                                      | 5   |

| 1.4 Outline of this Dissertation                      | 7   |

| CHAPTER 2 EMERGING NON-VOLATILE MEMORY AND LOGIC      | 9   |

| 2.1 Introduction                                      | 9   |

| 2.2 STT-MRAM Memory                                   | 9   |

| 2.2.1 Magnetic Tunnel Junction                        | 10  |

| 2.2.2 Tunnel Magnetoresistance                        | 11  |

| 2.2.3 MTJ Types                                       | 13  |

| 2.2.4 Spin Transfer Torque                            | 13  |

| 2.3 Nanomagnetic Logic                                | 15  |

| 2.3.1 Fundamental Concepts                            | 15  |

| 2.3.2 Logic and Interconnects                         | 17  |

| 2.3.3 Clock                                           | 19  |

| 2.3.4 Inputs and Outputs                              | 21  |

| 2.3.5 Concerns                                        | 21  |

| 2.4 Conclusion                                        | 22  |

| CHAPTER 3 STT-MRAM BASED LOGIC-IN-MEMORY ARCHITECTURE | 23  |

| 3.1 Introduction                                      | 23  |

| 3.2 Previous Work                                     | 24  |

| 3.3 Theory of STT-MRAM Based Logic Architecture       | 24  |

| 3.4 Design Challenges                                 | 25  |

| 3.5 CMOS Integration                                  | 26  |

| 3.6 Operation Techniques of the Architecture          | 28  |

| 3.7 Cell Types                                        | 28  |

| 3.8 Elementary Logic Blocks                           | 29  |

| 3.9     | Case Study: 2-input XOR                                       | 30 |

|---------|---------------------------------------------------------------|----|

|         | 3.9.1 Layout Description                                      | 30 |

| 3.10    | Conclusion                                                    | 32 |

| CHAPTER | 4 LOW POWER STT CLOCKING AND I/O INTERFACE                    | 33 |

| 4.1     | Introduction                                                  | 33 |

| 4.2     | Concept of STT Clock                                          | 33 |

| 4.3     | Spin Transfer Torque Write                                    | 36 |

| 4.4     | TMR Based Differential Read                                   | 38 |

|         | 4.4.1 Motivation                                              | 38 |

|         | 4.4.2 Variability Tolerant Differential Read                  | 39 |

|         | 4.4.3 Operation Principle                                     | 40 |

| 4.5     | Analysis of Read Circuit                                      | 42 |

| 4.6     | Conclusion                                                    | 43 |

| CHAPTER | 5 DEVICE MODELING AND LOW POWER EXTENSIONS                    | 44 |

| 5.1     | Motivation                                                    | 44 |

| 5.2     | Elemental Cell Modeling                                       | 44 |

|         | 5.2.1 Device Characteristics Modeling                         | 45 |

|         | 5.2.2 Neighbor Interaction Modeling                           | 45 |

| 5.3     | Low Energy Extensions of the Architecture and CMOS Comparison | 48 |

| 5.4     | Conclusion                                                    | 50 |

| CHAPTER | 6 SOLUTIONS TO HIGH DENSITY LOGIC                             | 51 |

| 6.1     | Motivation                                                    | 51 |

| 6.2     | Layout Constraint Problem                                     | 51 |

| 6.3     | Classical Example                                             | 53 |

| 6.4     | Novel Solution to the Problem                                 | 54 |

| 6.5     | High-Density Pipeline Problem                                 | 55 |

| 6.6     | Mathematical Description                                      | 57 |

| 6.7     | 3-phase Clock                                                 | 59 |

| 6.8     | 4-Phase Clock                                                 | 60 |

| 6.9     | Conclusion                                                    | 62 |

| CHAPTER | 7 LOGIC PARTITIONING                                          | 63 |

| 7.1     | Introduction                                                  | 63 |

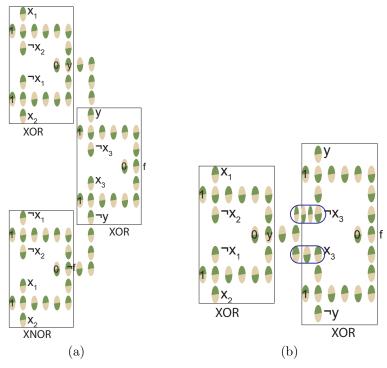

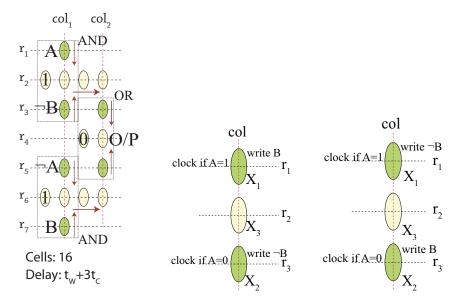

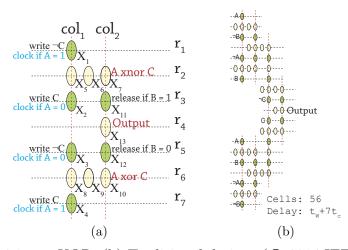

| 7.2     | Traditional XOR Design                                        | 63 |

| 7.3     | Theory Behind New Design                                      | 64 |

|         | 7.3.1 2-input XOR                                             | 65 |

|         | 7.3.2 3-input XOR                                             | 67 |

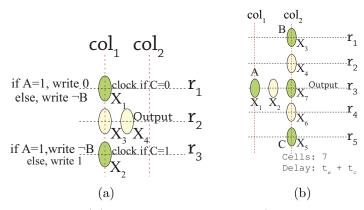

|         | 7.3.3 Novel Majority Design                                   | 67 |

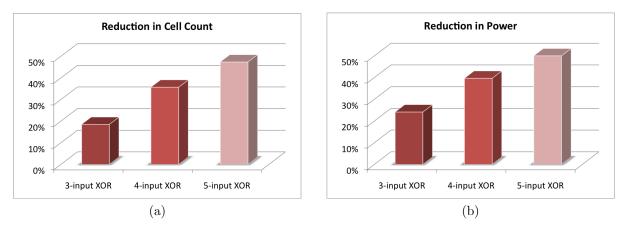

|         | 7.3.4 Analysis of the New Designs                             | 67 |

| 7.4     | Conclusion                                                    | 72 |

| CHAPTER  | 8 AUT      | HENTI     | CATION USING STT-MRAM                     | 75       |

|----------|------------|-----------|-------------------------------------------|----------|

| 8.1      | Motivation | on        |                                           | 75       |

| 8.2      | Physicall  | 75        |                                           |          |

|          | 8.2.1      | Memory    | Based PUFs                                | 76       |

| 8.3      | Theory o   | of MRAN   | M PUF                                     | 77       |

| 8.4      | MRAM 1     | PUF Op    | erating Principle                         | 78       |

| 8.5      | Sources of | of Bias a | and their Elimination                     | 79       |

| 8.6      | Destabili  | zation T  | Technique in STT-MRAM PUF                 | 81       |

| 8.7      | Results a  | and Ana   | lysis                                     | 82       |

|          | 8.7.1      | PUF Ev    | valuation                                 | 82       |

|          |            | 8.7.1.1   | Entropy                                   | 82       |

|          |            | 8.7.1.2   | Constructibility                          | 82       |

|          |            | 8.7.1.3   | Evaluability                              | 83       |

|          |            | 8.7.1.4   | Reproducibility                           | 83       |

|          |            | 8.7.1.5   | Uniqueness                                | 83       |

|          |            | 8.7.1.6   | Area                                      | 83       |

|          | 8.7.2      | Robusti   | ness Analysis                             | 84       |

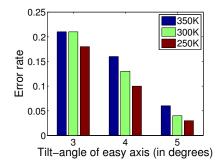

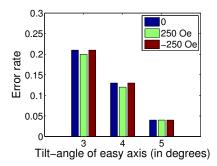

|          |            | 8.7.2.1   | Robustness with Temperature               | 85       |

|          |            | 8.7.2.2   | Robustness with Variations in Fixed Layer | 85       |

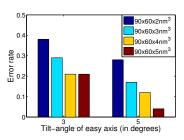

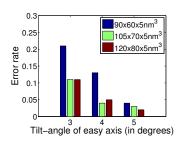

|          |            | 8.7.2.3   | Robustness Enhancement with Geometry      | 85       |

| 8.8      | Conclusio  | on        |                                           | 86       |

| CHAPTER  | 9 CON      | CLUSIC    | ON                                        | 87       |

| 9.1      | Synopsis   |           |                                           | 87       |

| 9.2      | Future V   | Vork      |                                           | 89       |

| REFEREN  | CES        |           |                                           | 90       |

| APPENDIC | CES        |           |                                           | 101      |

|          | endix A    | Copyrig   | ght Permissions                           | 102      |

| ABOUT TH | HE AUTE    | HOR       |                                           | End Page |

|          |            |           |                                           | U        |

# LIST OF TABLES

| Table 2.1 | MR improvement over the years.                                 | 13 |

|-----------|----------------------------------------------------------------|----|

| Table 2.2 | MTJ types.                                                     | 13 |

| Table 2.3 | Symbol definitions.                                            | 16 |

| Table 3.1 | Design rules of the architecture.                              | 26 |

| Table 3.2 | Metal pitch in the architecture.                               | 28 |

| Table 3.3 | Logic blocks in the 2-input XOR layout.                        | 31 |

| Table 4.1 | Comparison between STT write and field based write.            | 38 |

| Table 4.2 | Resistances for different read schemes in Fig. 4.2a.           | 42 |

| Table 5.1 | Device parameters used in simulation.                          | 45 |

| Table 5.2 | Ports of the multi-layered cell model.                         | 47 |

| Table 5.3 | Switching energy consumptions in fJ.                           | 50 |

| Table 5.4 | Leakage power consumption at 135°C.                            | 50 |

| Table 6.1 | Parameters used for solution.                                  | 55 |

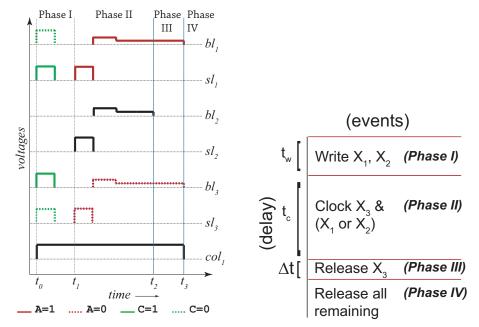

| Table 6.2 | Cell states in three consecutive time steps of 3-phase clock.  | 59 |

| Table 6.3 | Cell states in four consecutive time steps with 4-phase clock. | 61 |

| Table 6.4 | Delay and throughput from multiphase clock.                    | 62 |

| Table 7.1 | Cell count and delay comparison.                               | 69 |

| Table 7.2 | Current magnitudes and durations.                              | 70 |

| Table 7.3 | Energy consumption and EDP values.                             | 71 |

| Table 8.1 | PUF comparison.                                                | 84 |

# LIST OF FIGURES

| Figure 1.1 | Popular computer memories in different decades.              | 2  |

|------------|--------------------------------------------------------------|----|

| Figure 1.2 | Comparison of different memory technologies.                 | 4  |

| Figure 2.1 | (a) STT-MRAM architecture; (b) $1$ MTJ/ $1$ T STT-MRAM cell. | 10 |

| Figure 2.2 | MTJ states and structure.                                    | 11 |

| Figure 2.3 | Density of states for FM layers in 1 and 0 states.           | 12 |

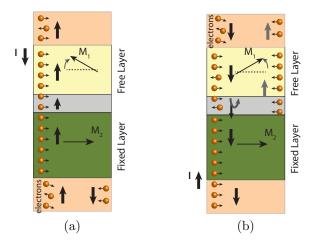

| Figure 2.4 | Theory of spin torque.                                       | 15 |

| Figure 2.5 | Torques on free layer during (a) write 0; (b) write 1.       | 15 |

| Figure 2.6 | Domains, logic states and coupling in nanomagnets.           | 17 |

| Figure 2.7 | Magnetic hysteresis and majority voter.                      | 18 |

| Figure 2.8 | Energy landscape and clock.                                  | 20 |

| Figure 3.1 | Architecture layouts.                                        | 27 |

| Figure 3.2 | A cross-section of a column.                                 | 27 |

| Figure 3.3 | 3D view of (a) a column; (b) a row.                          | 28 |

| Figure 3.4 | Layout of a 2-input XOR.                                     | 30 |

| Figure 4.1 | Input cell in logic-in-memory architecture.                  | 36 |

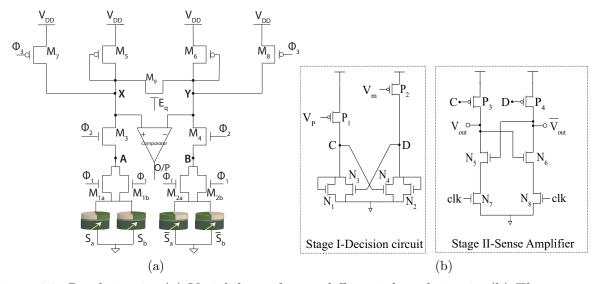

| Figure 4.2 | Read circuit.                                                | 40 |

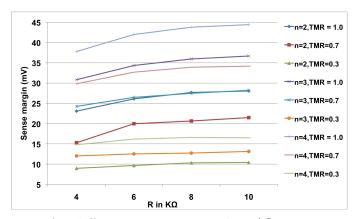

| Figure 4.3 | Sense margin for different $R_1$ , TMR and $n$ .             | 41 |

| Figure 4.4 | Comparison of reading techniques.                            | 42 |

| Figure 5.1 | Modeling neighbor interaction.                               | 46 |

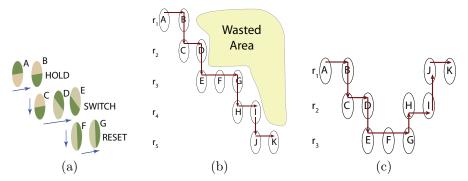

| Figure 6.1 | Explaining layout constraint.                                | 52 |

| Figure 6.2 | Solution to layout constraint problem.                       | 54 |

| Figure 6.3 | 3-input XOR.                                                        | 56 |

|------------|---------------------------------------------------------------------|----|

| Figure 6.4 | Improvement with introduction of selected irregularities.           | 56 |

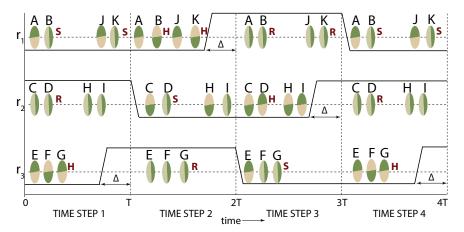

| Figure 6.5 | Logic states and staircase information propagation.                 | 57 |

| Figure 6.6 | 3-phase clock propagation.                                          | 58 |

| Figure 6.7 | 4-phase clock propagation.                                          | 61 |

| Figure 7.1 | 2-input XOR.                                                        | 64 |

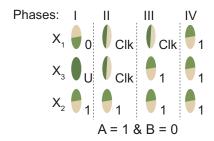

| Figure 7.2 | The top view of cells for $A=1$ and $B=0$ during different phases.  | 66 |

| Figure 7.3 | Voltage signals and delays.                                         | 66 |

| Figure 7.4 | (a) New 3-input XOR; (b) Traditional design.                        | 67 |

| Figure 7.5 | (a) New majority; (b) Traditional majority.                         | 68 |

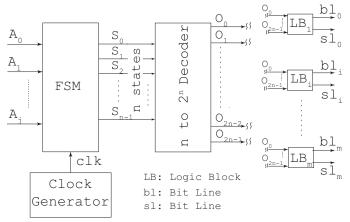

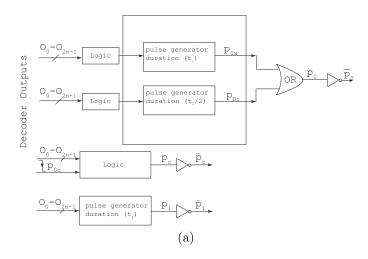

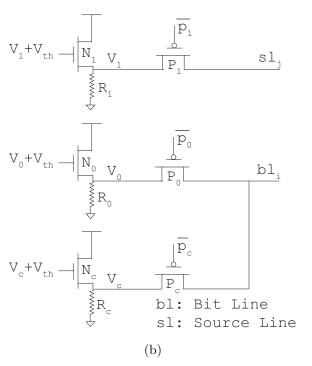

| Figure 7.6 | Block diagram of the CMOS peripherals.                              | 71 |

| Figure 7.7 | (a) The control signal generator; (b) The 3-level voltage shifter.  | 73 |

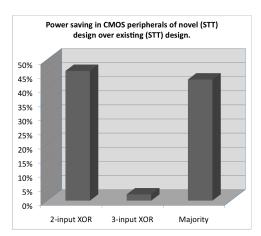

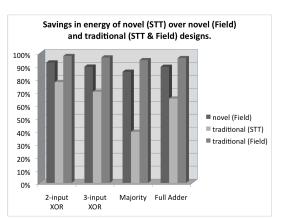

| Figure 7.8 | Power savings in CMOS peripherals.                                  | 74 |

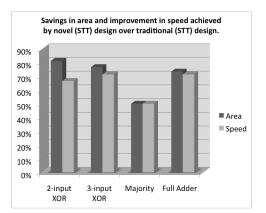

| Figure 7.9 | Performance improvement with logic partitioning.                    | 74 |

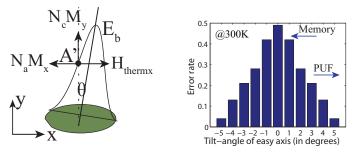

| Figure 8.1 | Energy landscape for different MTJ geometries                       | 78 |

| Figure 8.2 | Coupling with cell separation.                                      | 80 |

| Figure 8.3 | PUF operation and error rate.                                       | 81 |

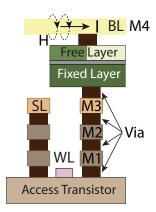

| Figure 8.4 | Cross-section of a STT-MRAM cell.                                   | 82 |

| Figure 8.5 | Error rate with temperature and variation in fixed layer thickness. | 84 |

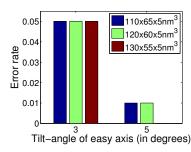

| Figure 8.6 | Error rate with different geometric variations                      | 86 |

#### ABSTRACT

Computer memories now play a key role in our everyday life given the increase in the number of connected smart devices and wearables. Recently post-CMOS memory technologies are gaining significant research attention along with the regular ones. Spin Transfer Torque Magnetoresistive RAM (STT-MRAM) is one such post-CMOS memory technology with a rapidly growing commercial interest and potential across diverse application platforms. Research has shown the ability of STT-MRAM to replace different levels of memory hierarchy as well. In brief, STT-MRAM possesses all the favorable properties of a universal memory technology. In this dissertation we have explored the roles of this emerging memory technology beyond traditional storage. The purpose is to enhance the overall performance of the application platform that STT-MRAM is a part of. The roles that we explored are computation and security. We have discussed how the intrinsic properties of STT-MRAM can be used for computation and authentication. The two properties that we are interested in are the dipolar coupling between the magnetic memory cells and the variations in the geometries of the memory cell. Our contributions here are a 22nm CMOS integrated STT-MRAM based logic-in-memory architecture and a geometric variation based STT-MRAM signature generation. In addition we have explored the device physics and the dynamics of STT-MRAM cells to propose a STT based clocking mechanism that is friendlier with the logic-in-memory setup. By investigating the logic layouts and propagation style in the architecture, we have also proposed different techniques that can improve the logic density and performance of the architecture.

#### CHAPTER 1

#### INTRODUCTION

## 1.1 Background

Memory is key to human consciousness and the linchpin of our identity [1]. Thomas Reid says "The evidence we have of our identity, as far back as we remember is grounded on memory." Memory has also continued to baffle our minds for centuries so much so that various attempts have been made to analyze it. Societies have also rested on its potentials for centuries to transmit texts with inordinate fidelity like the Vedas in Indian Literature. Some of the early references from Egypt and Greece (4000-1000BC) describes the governance of memory with gods and goddesses [2]. While the first documents of memory scholarship dates back to Dialexeis (5th century BC), it was not until Plato and Aristotle that memory was studied more theoretically. Plato used different metaphors like wax tablets and an aviary to describe the mechanisms of remembering and recalling. A few centuries later St. Augustine (354-430AD) compared memory to a cave with numerous mysterious recesses that are used to receive, store and retrieve information. He wonderfully proclaims "Great is the power of memory,...a large and boundless inner hall!" [2]. Philosophers have also not failed to recognize the fragility of this mystic human faculty. In the first century Pliny describes the susceptibility of memory to apprehensions, diseases and accidents. In the Renaissance period, the interest shifted more towards visual aids as Francis Bacon describes writing to be a great aid to memory. Among the other patrons of memory include poets and writers from different ages like Samuel Rogers, Emily Dickinson and Tony Morrison. The trend among modern psychologists is to use more contemporary examples like vibrating

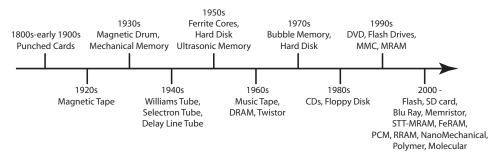

Figure 1.1: Popular computer memories in different decades.

particles, weathered signposts, electrical condensers and holograms to model memory. Very interestingly one of the recent models is after memory's greatest aid, the computer memory.

In computers the memory is that inner hall, which is used to store data and instructions. It is also a major decision maker to a computer's performance so much so that it has for decades driven scientists continually in the pursuit of various materials and technologies. With this continual effort the computer memory has not only grown in density over time, it has also significantly improved in speed. The punch cards that were popular in the early part of the twentieth century required hundreds of milliseconds to process a single card of less than 1Kb capacity [3, 4] while today's flash memories coming in finger-sizes can achieve a speed of 5 Gbps. Fig. 1.1 compiles a history of the development in computer memories [5, 6].

Today different memory technologies are investigated to meet different application demands. The worth of a memory technology is usually estimated with the help of certain key properties like cell size, access time, access mode, endurance, retention, power/energy, cost per bit, non-volatility and scalability. Here we will first discuss the property definitions before comparing some of the emerging memory technologies. The cell size defines the bit area in units of minimum feature size (F). Smaller the cell size, the denser is the memory. The access time refers to the read/write latency and the access mode refers to the random or block access of memory. Both impact the memory bandwidth. The endurance is the memory's ability to withstand the number of write, program, erase and read cycles. Retention refers to the length of time that a memory bit can hold onto its state. A memory technology

that can indefinitely hold onto its state without any external help is said to be non-volatile. The write energy for the memory is often the critical factor in the power/energy metrics of a memory technology and the usefulness of the technology. Cost per bit is a function that encompasses different aspects of technology like area, fabrication cost, testing, etc. Finally scalability refers to the scope for high density memories in future technology nodes and is one of the keys to cost reduction per bit. Fig. 1.2 compares different memory technologies on the basis of their above listed memory properties. From the figure it is obvious that the different memory technologies have a tradeoff between properties and the choice of a technology is therefore more application specific. However, in recent times technologies like Spin Transfer Torque Magnetoresistive RAM (STT-MRAM) have shown the potential to replace different levels of memory hierarchy [7] as a projected universal memory technology.

Memory is also fundamental to the vast majority of todays smart devices. It should not take any greater than a mere effort of simply imagining the horrors of losing all the contacts from our cell phones to appreciate the role of memories in our everyday modern life! Samsung the leader in smartphone mentions that consumer expectations of remaining "always-on always-connected" can only be enhanced by the advancement of the memory chip in the device [8]. Samsung is already looking into smart memories that can give high performance, greater energy savings and smaller form factor. Just as it has succeeded with philosophers and psychologists memory has continued to intrigue the minds of engineers and scientists as well. In this dissertation we have joined hands with this group of researchers to stretch the role of a contemporary memory technology beyond that of traditional data storage with the aim to improve the overall computing performance in modern devices.

#### 1.2 Motivation

As the advantages from Dennard scaling are nearing its end, Moore's law is also becoming more questionable in the forthcoming years. Industry and academics have therefore

|                              | Volatile                   |                   |                | Non-Volatile                          |                                                   |         |                                         |                                     |

|------------------------------|----------------------------|-------------------|----------------|---------------------------------------|---------------------------------------------------|---------|-----------------------------------------|-------------------------------------|

|                              | SRAM                       | DR<br>Stand-alone | AM<br>Embedded | Flash  NOR NAND  Embedded Stand-alone |                                                   | FeRAM   | STT-MRAM                                | PCM                                 |

| Storage Mechanism            | Interlocked<br>logic state | Charge in         | capacitor      |                                       | Trapped charge in floating gate or gate insulator |         | Magnetization of<br>ferromagnetic layer | Amorphous and<br>Crystalline phases |

| Cell Element                 | 6T                         | 1T                | 1C             | 1                                     | Т                                                 | 1T1C    | 1T1R                                    | 1T1R/1D1R                           |

| Feature Size, F, nm          | 45                         | 36                | 65             | 90                                    | 90 22                                             |         | 65                                      | 45                                  |

| Cell Area F^2                | 140                        | 6                 | 12-30          | 10                                    | 4                                                 | 22      | 20                                      | 4                                   |

| Read Time, ns                | 0.2                        | <10               | 2              | 15                                    | 1e5                                               | 40      | 35                                      | 12                                  |

| Write/Erase Time, ns         | 0.2                        | <10               | 2              | 1e3/1e7                               | 1e6/1e5                                           | 65      | 35                                      | 100                                 |

| Retention                    |                            | 64m               | 4m             | 10y                                   | 10y                                               | 10y     | >10y                                    | >10y                                |

| Endurance Cycles             | >1E16                      | >1E16             | >1E16          | 1E5                                   | 1E4                                               | 1E14    | >1E12                                   | 1E9                                 |

| Write Operating<br>Voltage V | 1                          | 2.5               | 2.5            | 10                                    | 15                                                | 1.3-3.3 | 1.8                                     | 3                                   |

| Read Operating<br>Voltage V  | 1                          | 1.8               | 1.7            | 1.8                                   | 1.8                                               | 1.3-3.3 | 1.8                                     | 1.2                                 |

| Write Energy J/bit           | 5E-16                      | 4E-15             | 5E-15          | 1E-10                                 | 2E-16                                             | 3E-14   | 2.5E-12                                 | 6E-12                               |

Figure 1.2: Comparison of different memory technologies [9].

got involved in seeking solutions from alternative technologies to meet the ever increasing consumer demands. STT-MRAM, Phase Change Memories (PCM) and Ferroelectric RAM (FeRAM) are some of the competing and promising non-volatile memory technologies listed by ITRS as technologies for future [10] (see Fig. 1.2). But what is so special about STT-MRAM? STT-MRAM is CMOS integrable. When compared to DRAM, STT-MRAM has a higher retention. When compared to SRAM it has a smaller footprint. And when compared to Flash and PCM, STT-MRAM provides unlimited read/write endurance. When compared to FeRAM it has a smaller feature size. In addition, STT-MRAM is also thermally robust and radiation hard [11]. It has also the potential to replace different levels of the memory hierarchy [7]. With its zero leakage property it can also help to develop sustainable platforms for various applications including data centers, which are currently plagued by excess leakage problems [12, 13].

STT-MRAM has already made its way to the market. 64Mb DDR3 compatible STT-MRAM and embedded MRAMs are already commercialized by Everspin Technologies, Inc. [11]. Toshiba has announced its first STT-MRAM based microprocessor cache memory [14]. In

their 2014 Emerging Non-Volatile Memory and Storage Technologies and Manufacturing Report, Coughlin Associates says "MRAM and STT-MRAM will start to replace SRAM and DRAM within the next few years. It is projected that MRAM and STT-MRAM annual shipping capacity will rise from an estimated 80 TB in 2013 to 16.5 PB in 2019 with revenues increasing over the same period from \$190 M to \$2.1 B." [15]. The thermal robustness and radiation hardness of MRAM has enabled the technology to be implemented from automobiles to outer space. These reports and properties strongly support the universal memory role that researchers have already started assigning to STT-MRAM [16, 17].

Convinced of its potential and universality, our objectives were to investigate this modern memory in unconventional roles beyond that of traditional storage. Our intention was to make the memory self sufficient in small computations and security related operations that can boost the overall performance of a smart device in this connected world. In this dissertation we have focused on using the intrinsic properties of STT-MRAM to design a logic-in-memory architecture and to generate unique digital signatures. While computation within memory can alleviate the Von Neumann bottleneck, a unique digital signature from the memory can combat some of the ever increasing concerns of security and piracy faced by the semiconductor industry. Here we have used the field coupling between closely spaced STT-MRAM cells for computation and the variation in the cell geometry for signature generation and authentication.

#### 1.3 Contribution

When it comes solely to data storage applications, the STT-MRAM cells are placed sufficiently far apart to prevent any interaction between them. By bringing the cells closer we risk interaction but open the scope for computation. In this dissertation we have used this concept to build a computing architecture with STT-MRAM. In memory every cell is integrated to a CMOS access transistor [16]. Reducing their spacing for computing purposes

now generates a pitch constraint from the underlying CMOS metal layer. In this dissertation we have discussed how to resolve this with 22nm CMOS technology and selective integration of access transistors. This logic-in-memory architecture we presented can switch between the logic and memory modes of operation with a clock signal as a classifier. The I/O operations for the architecture include write, clock and read. Here we have described how a CMOS operable low power STT clock can help to selectively clock the cells in the architecture. The clock is used to take the cells to a stationary state on top of the energy barrier that separates the two logical states at room temperature. We have shown that this stationary state can be achieved with the help of STT and a special configuration of the STT-MRAM cells that are already in active use in spin torque oscillators.

Our next I/O contributions include a variability tolerant differential read circuit that uses some of the intrinsic properties of the architecture and the cells. The STT-MRAM cells have different resistances for the 0 and 1 states. In memory their contents are read by comparing them to a reference value that is stored at the midpoint of the 0 and 1 resistances. Instead of reading a cell by comparing it to a reference value, we have proposed reading the output by comparing it to its complement that enhances the sense margin. Cell to cell interaction facilitates the complement generation and eliminates the cost associated with maintaining a precise reference. Further by replicating the output and its complement through coupling and comparing a pair of outputs against a pair of complements we have increased the variability tolerance of the read circuit.

To enable fast simulated verification of the architecture, we have designed Verilog-A macromodels to emulate the memory cells in standalone and computing modes of operation. The models internally run a Finite State Machine that decides the outcome of inter-cell coupling. Verilog-A also can be integrated into Cadence Design Suite and the memory cells can be simulated along with the CMOS access transistors. A common objective of the semiconductor industry is to reduce the logic footprint. Here we have discussed three different

ways in which we can reduce the logic footprint to enhance the overall computing performance of the architecture. The first is by introducing small irregularities in the otherwise regular logic layout. This solves a layout constraint problem, which originates from the inability of dipolar coupling to generate A and ¬A at a distance 'd' from a single variable A. A detailed study of the dipolar coupling based logic computation also reveals a constraint between delay, performance and flexibility of layout. By marginal increment in delay through an additional clock phase we have shown how performance and layout flexibility can be improved. Our next improvement is with the datapath elements. To enhance their performance in the architecture we have come up with a logic partitioning scheme based on Shannon expansion of logic. The algorithm efficiently partitions logic responsibilities between the magnetic and CMOS planes of the architecture. With the new partitioning only the cofactors are computed in the magnetic plane that reduces the footprint and improves the performance.

Finally in this dissertation we have shown how we can extract and digitize the information stored within the intrinsic geometric variations in the memory cells with the help of a simple two step procedure. The information can then be used as digital signatures that are unclonable and are not required to be stored anywhere in the memory. The signatures can help in authentication. The information can also be used for random number generation. We believe these roles supported by intrinsic STT-MRAM properties can boost the overall performance of STT-MRAM and the computing platforms.

#### 1.4 Outline of this Dissertation

The outline of this dissertation is as follows:

- (i) Chapter 2 gives a background of STT-MRAM and Nanomagnetic Logic (NML).

- (ii) Chapter 3 describes our logic-in-memory architecture, its salient features, its CMOS integration, cell types, logic blocks and logic layout.

- (iii) Chapter 4 describes the low power STT clock and CMOS powered write and read from the architecture. A variation tolerant differential read circuit is proposed that leverages from the bit dependency in the architecture.

- (iv) Chapter 5 describes a Finite State Machine based Verilog-A macromodel of the logic-in-memory cells that can be integrated to Cadence Design Suite and simulated with CMOS. It then proposes certain low energy extensions of the architecture.

- (v) Chapter 6 describes two schemes that can significantly reduce the logic footprint and improve the overall performance of the architecture.

- (vi) Chapter 7 describes a logic partitioning scheme between the magnetic and the CMOS planes of the architecture. The scheme is based on Shannon expansion of logic. The improvement in area, energy and delay of critical data path elements are discussed.

- (vii) Chapter 8 describes an intrinsic variation based signature generation scheme from STT-MRAM that can be used for autentication.

- (viii) Chapter 9 concludes this dissertation.

#### CHAPTER 2

#### EMERGING NON-VOLATILE MEMORY AND LOGIC

#### 2.1 Introduction

In this chapter we have reviewed the non-volatile STT-MRAM memory, its elemental cells and its key properties. Thereafter we have discussed nanomagnetic logic, a non-volatile logic technology. This chapter should help the readers to gain sufficient understanding of the memory and logic technologies to appreciate their integration in the later chapters of this dissertation.

## 2.2 STT-MRAM Memory

STT-MRAM is a class of recent non-volatile memories [11, 18, 19, 20, 21, 22]. Combined with the properties of thermal robustness, radiation hardness and unlimited endurance STT-MRAMs have often been projected as universal memories capable of replacing different levels of memory hierarchy [23]. They are already in use as critical storage in industry computing boards, flight control computers and superbike engine controls [11]. In 2012, Everspin Technologies, Inc. has commercialized 64Mb Spin-Torque MRAM [11]. STT-MRAM is also an active research area pursued by several semiconductor giants like Qualcomm Inc., Toshiba Corp., Fujitsu Ltd., Samsung, IBM Corp., Intel Corp. etc.

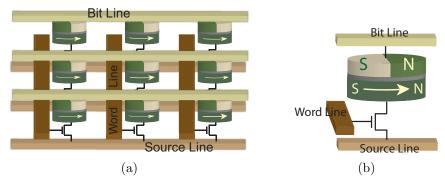

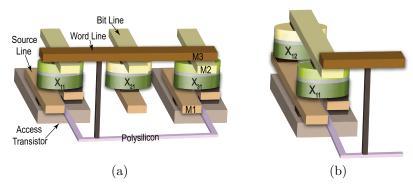

STT-MRAM has a crossbar memory architecture (see Fig. 2.1a(a)). Each bit is comprised of a magnetic tunnel junction (MTJ) monolithically integrated to an access transistor (see

<sup>&</sup>lt;sup>0</sup>Parts of this chapter was published in SPIN, World Scientific, 2014, vol. 4(3), "Recent Trends In Spintronics-Based Nanomagnetic Logic", Jayita Das, Syed M Alam, and Sanjukta Bhanja, editor Stuart Parkin. Permission attached in Appendix A.

Figure 2.1: (a) STT-MRAM architecture; (b) 1MTJ/1T STT-MRAM cell.

Fig. 2.1a(b)). Three layers of metal are used for bit-wise access to the memory. Two unique properties of MTJs are used for the two basic memory operations: (i) their response to spin transfer torque (STT) is used for memory write and (ii) their differential electrical resistance is used for memory read. In the following subsections we will focus on MTJs and their unique properties.

### 2.2.1 Magnetic Tunnel Junction

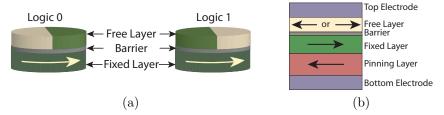

Magnetic Tunnel Junctions (MTJs) are multi-layered devices. They are composed of a thin insulating layer (barrier) sandwiched between two ferromagnetic (FM) layers (electrodes) [19, 24, 25, 26] (see Fig. 2.2a). The FM layers are single-domain, which means their magnetization is uniform and can be represented by one giant spin [27]. This property is enforced by the dimensions of the layer. The typical dimensions we used in this dissertation are  $100 \times 50 \text{ nm}^2$ . The MTJs are patterned with a shape anisotropy to generate two stable magnetic states for the FM layer at room temperature. These states are along the easy axis or the longest dimension of the layer. The magnetic polarization of the bottom FM layer is pinned by strong exchange coupling [28] from an adjacent antiferromagnetic layer such as FeMn or IrMn. This layer is called the fixed layer and the layer that pins it is called the pinning layer [21, 29, 30] (see Fig. 2.2b). The magnetization of the top FM layer can be excited with the help of external magnetic fields or with the help of STT [31, 32, 33, 34]

Figure 2.2: MTJ states and structure. (a) MTJ stable logic configurations (i) Parallel state; (ii) Antiparallel state; (b) MTJ structure and its main constituent layers.

(Section 2.2.4). This is called the free layer. With the help of relative magnetization between the free and the fixed layer, a 1 or 0 is stored in the memory (see Fig. 2.2a).

# 2.2.2 Tunnel Magnetoresistance

The MTJs also behave like a variable resistor. Their electrical resistance  $R=G(\theta)^{-1}$  depends on the relative magnetization angle  $\theta$  between the free and the fixed layer (Eq. 2.1) [22].

$$G(\theta) = \frac{1}{2} (G_P + G_{AP}) + \frac{1}{2} (G_P - G_{AP}) \cdot \cos \theta$$

(2.1)

$G_P$  and  $G_{AP}$  are the conductances for  $\theta = 0^\circ$  or parallel (logic 0) state (Fig. 2.2a(i)) and  $\theta = 180^\circ$  or antiparallel (logic 1) state (Fig. 2.2a (ii)). In MTJs,  $G_P$  (=  $R_P^{-1}$ ) >  $G_{AP}$  (=  $R_{AP}^{-1}$ ), and their difference  $\Delta$  G= $G_P$ - $G_{AP}$  is captured by the term Tunnel Magnetoresistance (TMR), defined in Eq. 2.2.

$$TMR = \frac{\Delta G}{G_{AP}} = \frac{R_{AP} - R_P}{R_P} \tag{2.2}$$

This difference in resistance is used to read the memory [19, 22]. High TMR is therefore suited for efficient memory read. Various sensing schemes have been developed where the MTJs are read by comparing against a reference value [35, 36, 37]. The reference is typically maintained at the midpoint of 0 and 1 resistances.

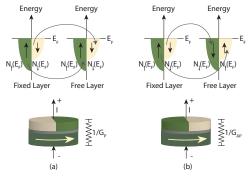

For the curious readers here we will slightly digress to explain the cause of TMR and summarize the milestones in its development. The difference in MTJ resistances for 1 and

0 states arise from the difference in the electronic density of states (DOS) at Fermi level  $E_F$  between the spin-up  $N_{\uparrow}(E_F)$  and the spin-down  $N_{\downarrow}(E_F)$  electrons [22]. Since tunneling preserves the electron spin orientation, electron tunneling between the two FM electrodes in MTJs takes place between spin subbands of the same orientation (see Fig. 2.3). The resultant tunneling conductance is therefore proportional to the product of the Fermi level DOS of the two electrodes with the same spin orientation [19, 22]. Since the DOS for the spin subbands is reversed for one of the electrodes between parallel and antiparallel configurations (see Fig. 2.3), the conductances of the two states differ from one another i.e.  $\Delta G \neq 0$ .

Figure 2.3: Density of states for FM layers in 1 and 0 states. For (a) parallel MTJ; (b) antiparallel MTJ. The net device conductance is proportional to the product of the density of states of the same spin for the fixed and the free layers.

TMR is a subset of the more generalized magnetoresistance (MR= $\Delta$  G/G) effect. When tunneling occurs across the barrier between the FM electrodes, as in MTJs, the phenomenon is called TMR. Interestingly the first MR phenomenon was discovered in 1856 [22, 38], but it was not until 1975 that Julliere [39] first defined it on a Fe/Ge/Co junction (Eq. 2.3).

$$\Delta G/G = 2P_1 P_2/(1 - P_1 P_2) \tag{2.3}$$

where,  $P_{1,2}$  are the spin polarization factors for the two FM electrodes [19, 22]

$$P_i = [N_{\uparrow}(E_F) - N_{\downarrow}(E_F)]/[N_{\uparrow}(E_F) + N_{\downarrow}(E_F)]$$

(2.4)

Julliere observed a MR ratio of 14% at 4.2K, which was not sufficient for any commercial application. Later experiments with different junction materials have helped to improve the MR (see Table 2.1).

Table 2.1: MR improvement over the years.

| Year                      | Device Junction                                              | MR value @ temperature |

|---------------------------|--------------------------------------------------------------|------------------------|

| Julliere[39], 1975        | Fe/Ge/Co                                                     | 14% @ 4.2K             |

| Miyazaki et al.[40], 1995 | $Fe/Al_2O_3/Fe$                                              | 18% @ RT*              |

| Bowen et al.[41], 2001    | Fe(001)/MgO/FeCo(001)                                        | 27% @ RT               |

| Kano et al.[42], 2002     | CoFeB/Al <sub>2</sub> O <sub>3</sub> /FeCo                   | 59.5% @ RT             |

| Parkin et al.[24], 2004   | $({\rm Co_{70}Fe_{30}})_{80}{\rm B_{20}/MgO/Co_{70}Fe_{30}}$ | 220% @ RT              |

| Yuasa et al.[43], 2006    | Co(001)/MgO(001)/Co(001)                                     | 410% @ RT              |

| Wang et al.[44], 2009     | $Co_2FeAl_{30}/MgO/Co_{75}Fe_{25}$                           | 700% @ 10K             |

# 2.2.3 MTJ Types

Depending on the plane of polarization of the free and the fixed layer, we have categorized MTJs into three types. Table 2.2 defines them, their properties, tradeoffs and applications.

Table 2.2: MTJ types.

| Type  | Definition                         | Figure     | Pros      | Cons                       | Applications |

|-------|------------------------------------|------------|-----------|----------------------------|--------------|

| i-MTJ | FL*: inplane; RL†: inplane         | <b>—</b>   | TMR: high | $I_{sw}^{\ddagger}$ : high | Memory       |

| p-MTJ | FL: out-of-plane; RL: out-of-plane | $\uparrow$ | TMR: med  | $I_{sw}$ : low             | Memory       |

| t-MTJ | FL: inplane; RL: tilted            |            | TMR: low  | $I_{sw}$ : med             | Oscillator   |

<sup>\*</sup>FL: Free layer, †RL: Reference layer or Fixed layer,  ${}^{\ddagger}I_{sw}$ : Switching current.

# 2.2.4 Spin Transfer Torque

Spin transfer torque (STT) originates when the spin of conduction electrons interacts with the local magnetic moment of a material [26, 45]. By transferring a part of their angular momentum to the magnet, the electrons directly apply a torque on the magnet. Exchange interactions rather than current induced magnetic fields are responsible for this

torque. With sufficient current, the torque can stimulate magnetic excitation or reverse the magnetization in the material.

STT is used in MTJs to switch the free layer. In MTJs, when a stream of electrons flow from the fixed to the free layer, majority gets oriented in the direction of the magnetic moment of the fixed layer by the time they leave the fixed layer. On reaching the free layer, they transfer their angular momentum, which results in a spin torque on the free layer trying to drive it to the parallel state [45] (see Fig. 2.4a). On the other hand, when a stream of electrons flow from the fixed to the free layer, they first get polarized by the free layer. When they strike the fixed layer only the ones with the same polarization as the fixed layer move through it. Electrons with opposite polarization get reflected and now exert a torque on the free layer that tends to drive it to the antiparallel state (see Fig. 2.4b). When the torque magnitudes are above a critical value, the free layer switches.

The equation governing the magnetodynamics of the free layer is given by Eq. 2.5.

$$\frac{d\mathbf{M}}{dt} = -\gamma \mathbf{M} \times \mathbf{H}_{eff} + \frac{\alpha}{M_s} \mathbf{M} \times \frac{d\mathbf{M}}{dt} + \frac{\gamma J_e G}{J_p} \mathbf{M} \times \mathbf{e}_{\mathbf{p}} \times \mathbf{M}$$

(2.5)

where,  $J_e$  is the current density through the MTJ and

$$G = \left[ -4 + (1+P)^3 \frac{(3+\hat{s_1}.\hat{s_2})}{4P^{3/2}} \right]^{-1}$$

(2.6)

$$J_p = \mu_0 \cdot M_s \frac{\mid e \mid t_F}{\gamma \hbar} \tag{2.7}$$

Table 2.3 defines the symbols. The first term on the right hand side of Eq. 2.5 defines the precession  $(\tau_H)$ , the second term defines the damping  $(\tau_d)$  and the third term defines the spin torque  $(\tau_{st})$ . During a write 0 the damping acts in the same direction as spin torque while during a write 1 the damping opposes the spin torque (see Fig. 2.5). Therefore current to write 0 is lesser than current to write 1. The critical write current  $I_{crit}$  to write the MTJ

Figure 2.4: Theory of spin torque. Electrons flowing from the (a) fixed to the free layer exerts spin transfer torque on the free layer that tends to drive it to the parallel state; (b) free to fixed layer gets reflected from the boundary of fixed layer and exerts a torque on the free layer that tends to drive it to the antiparallel state.

Figure 2.5: Torques on free layer during (a) write 0; (b) write 1.

is given by [46], where  $\pm$  is to write a 1 or 0. Note that the current  $I_{crit}$  scales with MTJ volume V.

$$I_{crit} = \frac{2e\alpha M_s V(H_K \pm H_{ext} + 2\pi M_s)}{\hbar \eta}$$

(2.8)

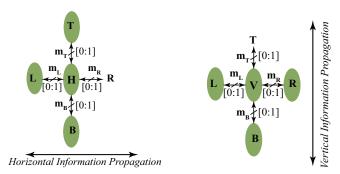

### 2.3 Nanomagnetic Logic

### 2.3.1 Fundamental Concepts

Nanomagnetic logic (NML) is a post-CMOS computing technology involving dipolar coupling between nanomagnets. The nanomagnets are sized for their single-domain behavior (see Fig. 2.6a). For lithographic limitations, most of the NML studies are conducted with

${\bf Table~2.3:~Symbol~definitions.}$

| Symbol                    | Description                                                                                                                                                                                                    |

|---------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| $\overline{a}$            | Aspect ratio of the cell.                                                                                                                                                                                      |

| $\alpha$                  | Gilbert damping constant.                                                                                                                                                                                      |

| d                         | Separation between cells.                                                                                                                                                                                      |

| e                         | Electron charge.                                                                                                                                                                                               |

| $\mathbf{e}_{\mathbf{p}}$ | Unit vector for magnetization along fixed layer.                                                                                                                                                               |

| $\eta$                    | Spin transfer efficiency.                                                                                                                                                                                      |

| $\gamma$                  | Gyromagnetic ratio.                                                                                                                                                                                            |

| $ m h_{eff}$              | Unit vector along effective magnetic field on the free layer arising. from crystalline and shape anisotropy, demagnetization field, exchange field and external field including coupling from the fixed layer. |

| $H_K$                     | Effective anisotropy field including magnetocrystalline anisotropy. and shape anisotropy.                                                                                                                      |

| $\hbar$                   | Reduced Planck's constant.                                                                                                                                                                                     |

| $K_U$                     | Anisotropy constant.                                                                                                                                                                                           |

| $m_1,\ m_2$               | Unit vectors in direction of magnetization of free and fixed layer.                                                                                                                                            |

| $M_s$                     | Saturation Magnetization.                                                                                                                                                                                      |

| $\mu_0$                   | Permeability of free space.                                                                                                                                                                                    |

| N                         | Demagnetization tensor.                                                                                                                                                                                        |

| P                         | Spin polarizing factor.                                                                                                                                                                                        |

| r                         | Radius of clock wire.                                                                                                                                                                                          |

| $\hat{s_1}, \ \hat{s_2}$  | Unit vectors along the global spin orientation of the free and fixed layers.                                                                                                                                   |

| $t_F$                     | Thickness of free layer.                                                                                                                                                                                       |

| V                         | Volume of free layer.                                                                                                                                                                                          |

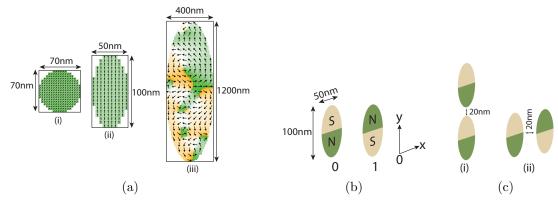

single-domain nanomagnets around 100nm in width and an aspect ratio of 2 [47, 48, 49]. A spacing of 20nm is typically chosen between nanomagnets to ensure effective dipolar coupling.

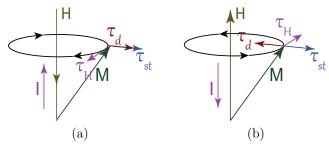

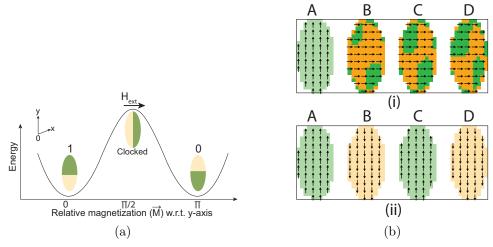

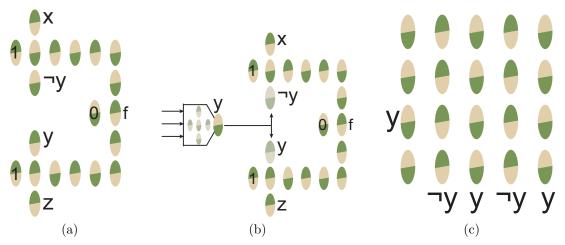

Figure 2.6: Domains, logic states and coupling in nanomagnets. (a) (i) Single-domain circular nanomagnet; (ii) Single-domain elliptical nanomagnet; (iii) Multiple-domain nanomagnet (Not drawn to scale). The simulations are carried out using Object Oriented MicroMagnetic Framework (OOMMF) [50]. (b) NML logic states. (c) Coupling between 20nm spaced nanomagnets: (i) Ferromagnetic coupling; (ii) Antiferromagnetic coupling.

Just like MTJs, the aspect ratio gives a shape anisotropy that generates two stable magnetization states along the easy axis at room temperature [51, 52]. The two states are used to represent 1 and 0 in logic. The two stable states are separated by an energy barrier, which is an unstable magnetization state and is also called the hard axis of the nanomagnet. Another important property of nanomagnets is their remanence, which is best explained by their hysteresis loop (see Fig. 2.7a). When there are no external magnetic fields acting on the nanomagnet, it continues to retain its previous state (position A and C in Fig. 2.7a). This accounts for the non-volatile behavior of NML.

#### 2.3.2 Logic and Interconnects

When two single-domain nanomagnets are placed around 20nm apart, they experience dipolar coupling. There are two types of coupling: (i) Ferromagnetic; and (ii) Antiferromagnetic. Two nanomagnets with their easy axis aligned will experience ferromagnetic

coupling (see Fig. 2.6c(i)) and with their easy axis in parallel will experience antiferromagnetic coupling (see Fig. 2.6c(ii)). Antiferromagnetic coupling functions as an inverter while ferromagnetic coupling functions as a buffer. Any logic function can be realized by combining the ferromagnetic and the antiferromagnetic coupling [51, 53].

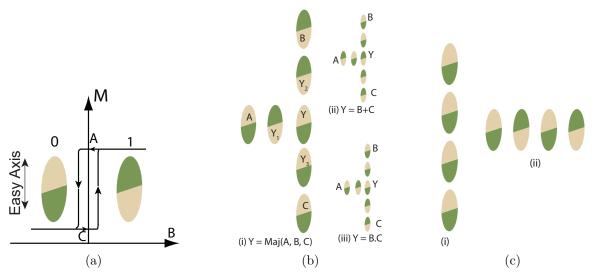

Fig. 2.7b shows a 3-input majority voter  $Y = A \cdot B + B \cdot C + C \cdot A$ . The output equals the majority of inputs through a series of ferromagnetic and antiferromagnetic coupling.  $Y_1$ ,  $Y_2$  and  $Y_3$  are the intermediary cells. In Fig. 2.7b we have worked out the logic for different input combinations. When A=1(0) the majority behaves as a 2-input OR(AND). Together with the inverter (Fig. 2.6c (ii)), the majority forms the universal minority function [54].

Figure 2.7: Magnetic hysteresis and majority voter. (a) Hysteresis in nanomagnets; (b) Majority voter, Y = M(A, B, C) = A.B + B.C + C.A. (i) Y = M(0, 1, 0) = 0 (ii) M(1, 0, 1) = B+C = 1 (iii) M(0, 0, 1) = B.C = 0. (c) (i) Ferromagnetic; and (ii) Antiferromagnetic wire.

Unlike logic, interconnects require only ferromagnetic or antiferromagnetic coupling (see Fig. 2.7c) [48]. Another interesting feature in NML is the crosswire formed of ferromagnetic coupling [49] where information can flow in orthogonal directions in a single plane. All these logic gates and wires have already been experimentally demonstrated [48, 49, 51, 55].

#### 2.3.3 Clock

The logic states in nanomagnets are separated by an energy barrier  $E_b$ . For a single-domain nanomagnet with uniaxial anisotropy,  $E_b$  is given by Eq. 2.9 [56].

$$E_b = \left(K_U + \frac{\mu_0 M_s^2 (1 - 3D)}{4}\right) V \tag{2.9}$$

where symbols are explained in Table 2.3. For an elliptical cross-section, the demagnetization factor D is roughly given by Eq. 2.10, where a is the aspect ratio and is > 1.

$$D = \frac{1}{2a+1} \tag{2.10}$$

For reasonable error probability  $e^{-(E_b/k_BT)} < e^{-30}$ , which means  $E_b \ge 30k_BT$  [57]. For nanomagnet dimensions of  $100 \times 50 \times 2$  nm<sup>3</sup>, the energy barrier  $E_b \approx K_U V > 1200 k_BT$ . This ensures the stability of logic states at room temperature. However, when we want to compute we want the nanomagnets to couple and settle for their new ground states. The dipole-dipole interaction energy of nanomagnets is given by Eq. 2.11 [57]. For ferromagnetic and antiferromagnetic coupling, the coupling energy is given by Eq. 2.12.

$$E_{dipole-dipole}^{i-j} = \frac{\mu_0 M_s^2 V^2}{4\pi |\overrightarrow{d}_{i-j}|^3} \left[ \overrightarrow{m}_i \cdot \overrightarrow{m}_j - \frac{3}{|\overrightarrow{d}_{i-j}|^2} (\overrightarrow{m}_i \cdot \overrightarrow{d}_{i-j}) (\overrightarrow{m}_i \cdot \overrightarrow{d}_{i-j}) \right]$$

(2.11)

$$E_{dipole-dipole} = \frac{\mu_0 M_s^2 V^2}{4\pi d^3} \tag{2.12}$$

For  $100 \times 50 \times 2$ nm<sup>3</sup> nanomagnets with 20nm spacing the ferromagnetic and antiferromagnetic coupling energies are  $0.896k_BT$  and  $4.48k_BT$ , none of which are sufficient to flip the state of the nanomagnets. Therefore to compute with nanomagnets, we need an extra force that can help to cross the barrier but not impact the direction of crossing the barrier. In practice we need a force that takes the nanomagnets to their hard axis from where coupling takes over.

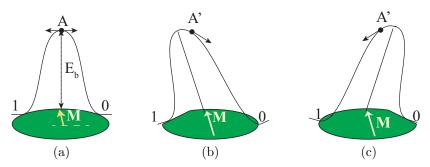

Figure 2.8: Energy landscape and clock. (a) Energy landscape in nanomagnets; (b) (i) t = 0 state of a clocked antiferromagnetic wire. A is the input while B, C, D are clocked; (ii) final state of the wire after clock is released. The simulations were run using OOMMF software.

In NML this is called the clock, which is an external field directed along the hard axis of nanomagnets (see Fig. 2.8a(a)) in order to destabilize them. When the clock is released, the nanomagnets reorient according to the coupling from their neighbors (see Fig. 2.8b).

The early implementations of clock were slowly increasing external fields also called pumping fields directed along the hard axis of the nanomagnets. These fields were then slowly reduced to zero. If the pumping process is slow enough, typically in MHz, the switching becomes adiabatic in nature [58]. More recently an on-chip clock field generation scheme was introduced [59] where copper wires cladded with ferromagnetic wires were used. The wires were placed underneath the nanomagnets and could clock 100-1000 nanomagnets together. The required clock field  $H_{req}$ , current density  $J_{clk}$  and nanomagnet dimensions V are related by Eq. 2.13, where r is the radius of the wire [57].

$$H_{req} = \frac{E_b}{\mu_0 M_s V} = \frac{J_{clk} r}{2} \tag{2.13}$$

For a nanomagnet of dimension  $100 \times 50 \times 2$ nm<sup>3</sup> and a clock wire of radius 200nm the clocking current is 10mA. To reduce the clocking current, clocking structure with enhanced

permeability dielectric (EPD) films surrounding the dielectric has been proposed [60]. Apart from high clocking current some other drawbacks of this field induced clock are: (i) non-scalability of clock current  $J_{clk} \propto 1/V$ ; and (ii) no cell selectivity or individual nanomagnets cannot be selected from a group for clocking. More recently researchers have proposed and demonstrated the use of strong localized in-plane magnetic fields generated by domain walls superposed with externally applied fields for clocking and switching nanomagnets [61, 62]. For a 200ms<sup>-1</sup> propagating domain wall, a current density of  $2 \times 10^{12} \text{Am}^{-2}$  is required [63], which is equivalent to a current of 3.6mA for a typical  $100 \times 18 \text{nm}^2$  domain wall conductor. The current requirements for clocking are therefore still high.

### 2.3.4 Inputs and Outputs

Initially off-chip standard moment magnetic force microscopy (MFM) probe was used to write and read from NML [49]. Based on simulation results on-chip writing technique using fields generated by the free layer of MTJs have been proposed [64]. Possible reading techniques have also been proposed using inductive methods, capacitive methods and MTJs [23]. Recently MTJ based magnetoresistive read of single-layer nanomagnets [65] has been experimentally demonstrated. Other possible writing techniques involve keeping the ferromagnet in contact to a multiferroic layer and applying an electric field to the ferromagnet/multiferroic heterostructure [66].

#### 2.3.5 Concerns

Some of the concerns of NML include:

- (i) mA range clocking current;

- (ii) non-scalability of clock;

- (iii) lack of reliable on-chip read and write techniques;

- (iv) lack of selectivity over logic cells;

- (v) lack of CMOS user interface for on-chip automation;

- (vi) random and repeatable errors in nanomagnet chains from process variations [67].

#### 2.4 Conclusion

In this chapter we have discussed STT-MRAM and the key properties of MTJs. We studied the MTJ structure and the concept of TMR. Thereafter we studied the theory of STT and the mechanism of STT based write in MTJs. Next we discussed NML, a post-CMOS magnetic dipolar-coupling based non-volatile logic technology. We described the elemental logic cells and the two types of coupling. We then discussed the fundamentals of coupling based computation and the necessity of clocking. We concluded this chapter with some of the concerns of NML. In the next chapters we will describe the ways we have married the two technologies to demonstrate the ability of STT-MRAM in unconventional roles for modern computing devices.

#### CHAPTER 3

#### STT-MRAM BASED LOGIC-IN-MEMORY ARCHITECTURE

#### 3.1 Introduction

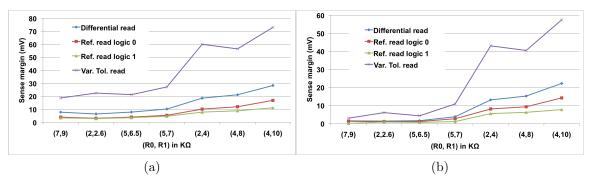

In the last chapter we studied some of the properties of STT-MRAM that makes it one of the promising non-volatile memory technologies of today. In this chapter we will discuss how some of these properties can be used to extend the role of STT-MRAM into computing. As we discussed in Section 2.2, the elemental cell of STT-MRAM is magnetic and is monolithically integrated to CMOS. It can be written with the help of STT and can be read with the help of TMR. We have also discussed under Section 2.3 a post-CMOS zero-leakage magnetic logic technology that uses dipolar coupling between magnetic cells to compute logic. In this chapter we will discuss how STT-MRAM technology can readily import some of the NML concepts. We have then used this property to design a sustainable non-volatile logic-in-memory platform.

Such a non-volatile platform or architecture as we will interchangeably call in this dissertation can help to save several initialization cycles in CPU [68]. It can also help to reduce leakage and aid in fine grain power gating [69, 70]. Such power savings are critical for sustainable computing and battery powered platforms. The savings in leakage becomes even more significant at high temperatures that are common in automobiles. In this non-volatile logic-in-memory architecture we have used NML style for computation and STT-MRAM style for

<sup>&</sup>lt;sup>0</sup>This chapter was published in IEEE Transactions on Circuits and Systems I: Regular Papers, vol. 59(9): pp. 2008-2016, 2012, "Ultra-low Power Hybrid CMOS-Magnetic Logic Architecture", Jayita Das, Syed M Alam, and Sanjukta Bhanja. Permission attached in Appendix A and

<sup>11</sup>th IEEE Conference on Nanotechnology (IEEE-NANO), pp. 1261-1266, 2011, "Low power cmos-magnetic nano-logic with increased bit controllability", Jayita Das, Syed M Alam, and Sanjukta Bhanja. Permission attached in Appendix A.

read and write. For clock we have used a new style that we have discussed in Chapter 4. In this chapter we have discussed the design challenges of the architecture, the key features, the elementary cell types and the operation techniques of the architecture. In the next section we will briefly review some existing non-volatile MTJ based logic for completeness before going into the architecture details.

#### 3.2 Previous Work

Wang et al. in 2005 [71] demonstrated 2-input non-volatile logic functions based on magnetic field and thermally induced switching of MTJs. AND, OR, NOR, NAND, XOR, XNOR were demonstrated. Their main drawbacks were high currents of around 70mA and low MR of around 14%. Ikeda et al. developed 2-input logic functions by a parallel combination of MTJs and CMOS transistors [72]. In the logic one input was stored in the MTJs and the other was directly applied to the CMOS transistors. Here the MR of MTJs were used to calculate the logic output. Matsunaga et al. demonstrated 3-input circuits like MTJ based full adders in 2008 [73]. Researchers have also explored non-volatile programmable logic functions using MTJ/CMOS based LUTs [17, 74, 75]. However, none to our knowledge have used dipolar coupling between MTJs for logic computation.

### 3.3 Theory of STT-MRAM Based Logic Architecture

As we discussed in Section 2.2.1, the free layer and the fixed layer in MTJs are ferromagnetic and single-domain. However, only the free layer can switch. When MTJs are within 20nm of one another their free layers can also couple. The coupling can be either ferromagnetic or antiferromagnetic (see Fig. 2.6c). We have also validated the coupling through simulations and fabrications [76, 77]. Here we have used this coupling between free layers to design our computing platform [78, 79]. Our chosen MTJ dimensions are  $100 \times 50 \text{nm}^2$  and their spacing is 20nm. This is also the same as in NML.

Just like single-layered nanomagnets the MTJs are patterned with a shape anisotropy. As a result the ground states in their free layers are separated by an energy barrier  $E_b$ , which determines their thermal stability or bit stability at room temperature. As we have seen in Section 2.3.3, an  $E_b \geq 30k_BT$  is required to maintain high bit stability. We have also seen that the energy from coupling is not sufficient to help a magnet to cross over the barrier. Therefore, like NML a clock signal is required to assist coupling based computation in MTJs. The clock can be an external magnetic field directed along the hard axis of MTJs. However, as we have seen in Section 2.3.3 a field based clock requires high current and is not scalable. To build a sustainable computing platform we therefore need a low power clock. In Section 4.2 we have proposed a novel spin transfer torque (STT) based clock for MTJs. The clock current is much lesser than field-induced clock. It is also scalable. Like in memory we have used STT to write inputs into the architecture (Section 4.3). In Section 2.2.2 we have already studied the phenomenon of TMR and in Section 4.4 we have proposed a onchip variability tolerant TMR based differential read scheme for the architecture. The TMR based read scheme is also low power. Finally with CMOS integration we aim to achieve fine-grain selection of cells, which can reduce the random errors in nanomagnetic chain [80].

### 3.4 Design Challenges

The design challenges for the architecture arose from the need to fulfill the conflicting technical requirements discussed below:

- (i) A regular cell layout;

- (ii) Cell size between thermal stability and single-domain limits;

- (iii) Maximum integration of access transistors;

- (iv) 20nm spacing between MTJs;

- (v) Metal pitch of CMOS technology;

- (vi) Sufficient drive capability of access transistors; and

- (vii) Minimum metal layers for low cost implementation.

We resolved the challenges by [81, 82]:

- (i) Choosing  $100 \times 50 \text{nm}^2$  cross-section cells;

- (ii) Selecting 22nm CMOS technology node;

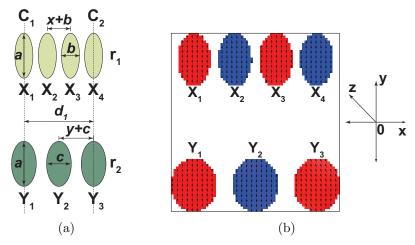

- (iii) Integrating one access transistors for every 2×2 STT-MRAM cell arrays (see Fig. 3.1a).

Table 3.1 compiles the design rules for the architecture.

Table 3.1: Design rules of the architecture.

| Parameters         | Design Rule                  |

|--------------------|------------------------------|

| Cell cross-section | $100 \times 50 \text{nm}^2$  |

| Row pitch          | 70nm                         |

| Column pitch       | 120nm                        |

| Access transistor  | one every $2 \times 2$ array |

# 3.5 CMOS Integration

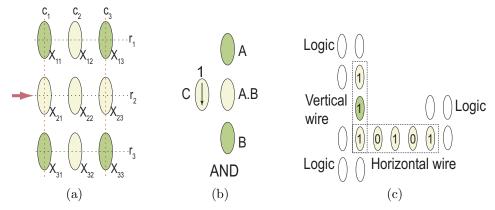

Fig. 3.1a shows the integration of access transistors. Only alternate MTJs in a row or column can have access transistor. The architecture is regular with three layers of metal like memory. Fig. 3.1b and Fig. 3.1c shows logic gates and cell interconnects in the architecture. Fig. 3.2 shows a cross-section of the architecture along column  $c_1$  of Fig. 3.1a. The sourcelines and bitlines are in metal M1 and M2 respectively. They run parallel to the rows. The wordlines are in metal M3 (see Fig. 3.3a). They run parallel to the columns. The sourcelines are either connected to the source of access transistors (e.g.  $X_{11}$ ) or to the fixed layer of MTJs that are without access transistors (e.g.  $X_{12}$ ). The bitlines are connected to the free layer of MTJs. The wordlines are connected to the gates of the access transistors. Table 3.2 summarizes the metal pitch in the architecture and the CMOS 22nm technology

Figure 3.1: Architecture layouts. (a) The regular architecture layout with green MTJs integrated with access transistor and yellow MTJs without access transistors. (b) MTJ layouts for two-input AND. Cell C is fixed to 1. (c) Vertical and horizontal wires. (© 2012 IEEE, with permission.)

Figure 3.2: A cross-section of a column. (© 2012 IEEE, with permission.)

requirements. Fig. 3.3a shows a 3D view of a column and Fig. 3.3b shows a 3D view of a row in the architecture.

To summarize, the salient design features of the architecture are:

- (i) It is regular;

- (ii) An access transistor for every  $2 \times 2$  MTJ array;

- (iii) Three layers of metal lines operating the cells;

- (iv) A sourceline and bitline for every row and a wordline for every alternate column.

Table 3.2: Metal pitch in the architecture. (© 2012 IEEE, with permission.)

| Metal Layer | Control Line | Architecture Pitch | Required 22nm CMOS pitch [83] |  |  |

|-------------|--------------|--------------------|-------------------------------|--|--|

| Metal 1     | Sourceline   | 70nm               | 64nm                          |  |  |

| Metal 2     | Bitline      | 120nm              | > 64nm                        |  |  |

| Metal 3     | Wordline     | 140nm              | > 64nm                        |  |  |

Figure 3.3: 3D view of (a) a column; (b) a row. (© 2012 IEEE, with permission.)

### 3.6 Operation Techniques of the Architecture

The MTJs in the architecture are to be written or clocked with STT. We have already discussed the theory of STT write in Section 2.2.4 and we will be discussing the theory of STT clock in Section 4.2. In this section we will briefly discuss the CMOS operations during write and clock. The write technique is very similar to STT-MRAM. Only MTJs with access transistors are to be written. During write the required potential is to be applied across the bitline and sourceline of the MTJ to be written and the corresponding wordline needs to be activated. Clocking is similar. The appropriate potential is to be applied across the bitline and sourceline of the MTJs and corresponding wordlines (if present) need to be activated.

### 3.7 Cell Types

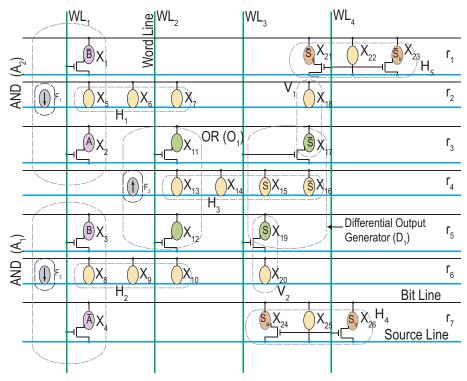

We have divided the architecture cells into three broad types based on their responsibilities. With the help of the layout of a 2-input XOR (see Fig. 3.4), we have explained the cell functions and their placements in the architecture.

- (i) Input Cells: These MTJs are the inputs to logic gates and are only written. They should always have access transistors and are never clocked. A, B, ¬A and ¬B are the input cells in Fig. 3.4. They are marked in pink.

- (ii) Output Cells: These MTJs hold the outputs of logic. They have access transistors and are both clocked and read. The output cells in Fig. 3.4 are marked in orange.

- (iii) Logic Cells: These MTJs form the body of logic and the actual computation takes place in these cells. These MTJs are only clocked and are never written nor read. We have further classified them into: