### DIGITAL COMMONS © UNIVERSITY OF SOUTH FLORIDA

University of South Florida Digital Commons @ University of South Florida

USF Tampa Graduate Theses and Dissertations

USF Graduate Theses and Dissertations

3-25-2004

# Investigation Of Oxide Thickness Dependence Of Fowler-Nordheim Parameter B

Shashank Bharadwaj University of South Florida

Follow this and additional works at: https://digitalcommons.usf.edu/etd

Part of the American Studies Commons

#### Scholar Commons Citation

Bharadwaj, Shashank, "Investigation Of Oxide Thickness Dependence Of Fowler-Nordheim Parameter B" (2004). USF Tampa Graduate Theses and Dissertations. https://digitalcommons.usf.edu/etd/959

This Thesis is brought to you for free and open access by the USF Graduate Theses and Dissertations at Digital Commons @ University of South Florida. It has been accepted for inclusion in USF Tampa Graduate Theses and Dissertations by an authorized administrator of Digital Commons @ University of South Florida. For more information, please contact digitalcommons@usf.edu.

#### Investigation Of Oxide Thickness Dependence Of Fowler-Nordheim Parameter B

by

Shashank Bharadwaj

A thesis submitted in partial fulfillment of the requirements for the degree of Master of Science in Electrical Engineering Department of Electrical Engineering College of Engineering University of South Florida

Major Professor: Dr. Yun Lee Chiou, Ph.D. Dr. Wilfrido A. Moreno, Ph.D. Dr. Christos Ferekides, Ph.D.

> Date of Approval: March 25, 2004

Keywords: i-v characteristics, c-v characteristics, nvm, tunneling, scaling

© Copyright 2004, Shashank Bharadwaj

#### ACKNOWLEDGEMENT

I owe my grateful acknowledgement to Dr. Chiou for his invaluable guidance and constant encouragement over the course of time spent in this research effort. Finally, he poured every inch of the report with painstaking attention to detail and offered extremely useful comments.

My special thanks are due to Professor Ferekides and Professor Moreno for serving on my committee.

I would also like to thank Mehdi Mansouri and Surendra for all their help during the course of this research work. A special thanks to Sharp Laboratories of America, Inc. for providing our lab with the wafers, without which this research work would not have been possible.

Lastly, I would like to put on record my appreciation for the patience, encouragement, and indulgence of my parents, my sister and my wife.

## **Table of Contents**

| List of Tables                                                    | iv   |

|-------------------------------------------------------------------|------|

| List of Figures                                                   | v    |

| Abstract                                                          | viii |

| Chapter 1. Introduction                                           | 1    |

| 1.1 Gate Dielectrics                                              | 2    |

| 1.2 High K Dielectric                                             | 4    |

| 1.3 Future Trends in Silicon Technology and Purpose of the Thesis | 5    |

| Chapter 2. MOS Devices                                            | 8    |

| 2.1 Ideal MOS Diode                                               | 8    |

| 2.1.1 Threshold Voltage                                           | 12   |

| 2.1.2 MOS Capacitor under Bias                                    | 13   |

| 2.1.2.1 Surface Accumulation                                      | 15   |

| 2.1.2.2 Surface Depletion ( $V_T < V_{GB} < V_{FB}$ )             | 16   |

| 2.1.2.3 Surface Inversion ( $V_T > V_{GB}$ )                      | 17   |

| 2.1.3 Non Ideal MOS Capacitor                                     | 18   |

| 2.2 MOSFET                                                        | 22   |

| 2.2.1 Basic Structure and Principle of Operation of the MOSFET    | 22   |

| 2.2.2 Current-Voltage Characteristics of the MOSFET               | 24   |

| 2.2.3 Importance of MOSFET                                        | 26   |

| 2.3 Non Volatile Memory (NVM)                                     | 27   |

| 2.3.1 Structure of a Typical Floating Gate Device                 | 28   |

| 2.3.2 Operation Conditions                                        | 28   |

| 2.3.2.1 Write Operation                                           | 29   |

| 2.3.2.2 Erase Operation                                           | 30   |

| 2.4 MOS Device Scaling                                            | 31   |

| Chapter 3. Characterization of Thin Gate Oxide                    | 34   |

| 3.1 Introduction                                                  | 34   |

| 3.2 Current Conduction Mechanism                                  | 35   |

| 3.2.1 Thermionic Emission                                         | 36   |

| 3.2.2 Fowler-Nordheim Tunneling                                   | 36   |

| 3.2.3 Direct Tunneling                                            | 38   |

| 3.2.4 Analytical Expressions for the Tunnel Currents              | 39   |

|                                                                   |      |

| 3.3 Dielectric Breakdown                                       | 41 |

|----------------------------------------------------------------|----|

| 3.3.1 Time Dependent Dielectric Breakdown (TDDB)               | 42 |

| 3.3.2 Dielectric Breakdown Models                              | 43 |

| 3.3.2.1 Bandgap Ionization Model                               | 44 |

| 3.3.2.2 Anode Hole Injection Model                             | 45 |

| 3.3.2.3 Hydrogen Release Model                                 | 45 |

| 3.4 Reliabilty                                                 | 46 |

| 3.4.1 Reliability Projections                                  | 48 |

| Chapter 4. Determination and Extraction of Parameter B         | 50 |

| 4.1 Introduction                                               | 50 |

| 4.2 Importance of Parameter B                                  | 51 |

| 4.3 Sample Fabrication                                         | 51 |

| 4.4 Measurement Setup                                          | 52 |

| 4.4.1 Overview of Equipments                                   | 53 |

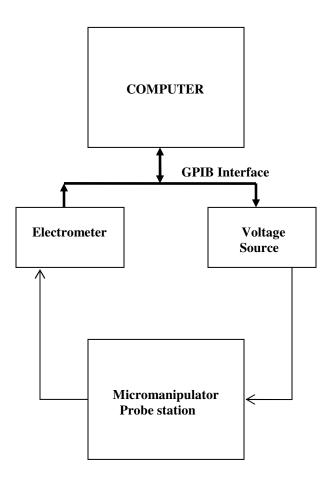

| 4.4.2 Lab Setup for I-V Measurements                           | 54 |

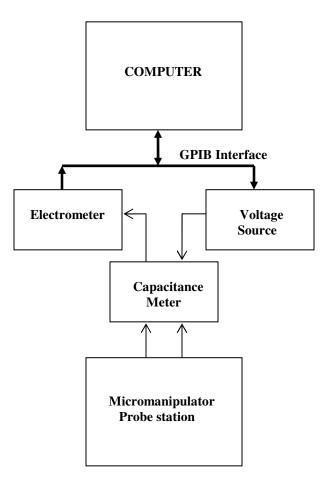

| 4.4.3 Lab Setup for C-V Measurements                           | 56 |

| 4.5 Analysis                                                   | 57 |

| 4.5.1 Time Dependent Dielectric Breakdown (TDDB)               | 59 |

| 4.5.2 F-N Region                                               | 61 |

| 4.5.2.1 C-V Characteristics                                    | 61 |

| 4.5.2.2 I-V Characteristics                                    | 64 |

| 4.5.2.3 F-N Slope Analysis and Experimental Results            | 67 |

| Chapter 5. Summary and Conclusion                              | 71 |

| References                                                     | 74 |

| Appendices                                                     | 78 |

| Appendix A Factors Affecting Testing on Probe Station          | 79 |

| A.1 Random Noise Introduction                                  | 79 |

| A.2 Periodic Noise Introduction                                | 79 |

| A.3 Noise Coupled Through Measurement Equipment                | 79 |

| A.4 Probe Contact                                              | 80 |

| A.5 Leaky Probes                                               | 80 |

| A.6 Factor Affecting the Low Level Environment Current Testing | 80 |

| A.6.1 Common Impedance                                         | 80 |

| A.6.1.1 Preventive Measure                                     | 81 |

| A.6.2 Magnetically Coupled Noise                               | 81 |

| A.6.2.1 Preventive Measure                                     | 81 |

| A.6.3 Incidental Capacitive Coupling                           | 81 |

| A.6.3.1 Preventive Measures                                    | 82 |

| A.6.4 Charge Transfer                                          | 82 |

| A.6.4.1 Preventive Measure                                     | 82 |

| A.6.5 Light                                                    | 82 |

| A.6.5.1 Preventive Measures                                     | 82 |

|-----------------------------------------------------------------|----|

| A.6.6 Intrinsic Noise Sources                                   | 83 |

| A.6.6.1 Preventive Measures                                     | 83 |

| A.6.7 Leakage Current                                           | 83 |

| A.6.7.1 Preventive Measures                                     | 83 |

| A.7 Work Done on the Probe Station in Noise and Reliability Lab | 83 |

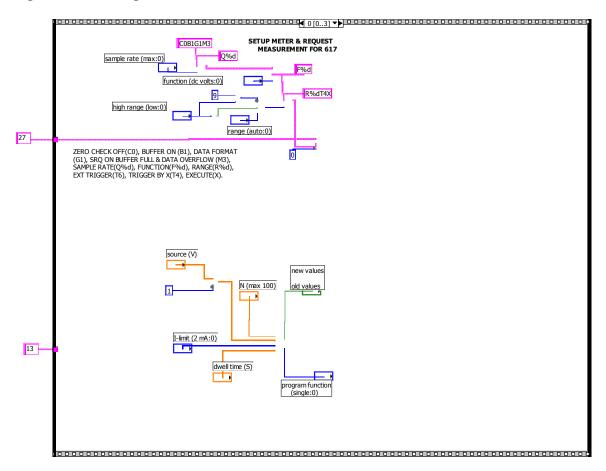

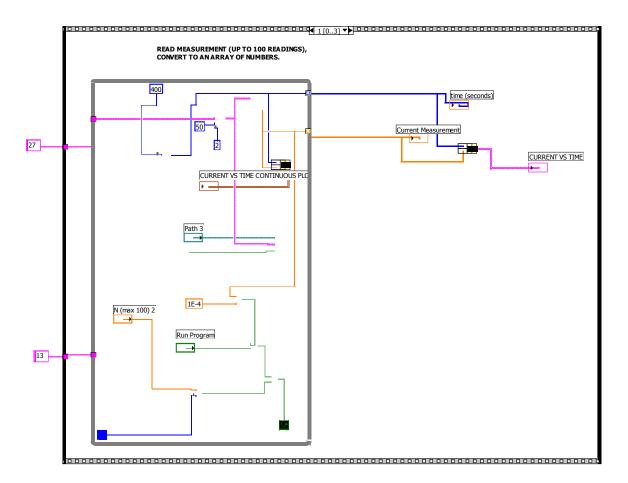

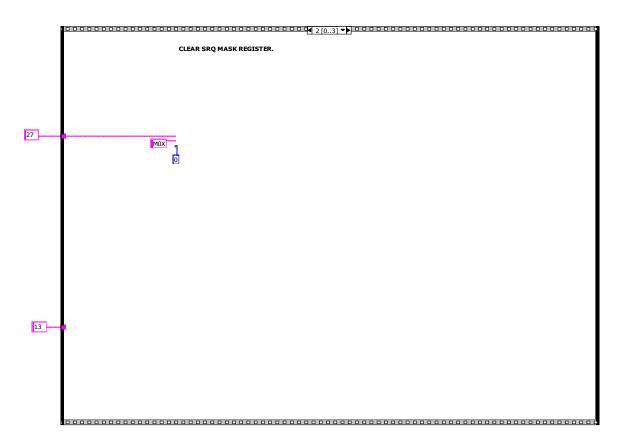

| Appendix B LabVIEW and Integrated Circuit Testing               | 85 |

| B.1 Introduction                                                | 85 |

| B.2 Front panel of the VI                                       | 86 |

| B.3 Block diagram of the VI                                     | 87 |

| B.4 How to run the program                                      | 89 |

|                                                                 |    |

## List of Tables

| Table 2.1 | Source, Drain and Control Gate Biases for Operation of a Typical Flash<br>Call | 28 |

|-----------|--------------------------------------------------------------------------------|----|

| Table 2.2 | Historical Trends in Scaling                                                   | 31 |

## List of Figures

| Figure 1.1  | Predictions for the Next Few Generations of Chips                                                                                                                                                                      | 3  |

|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Figure 1.2  | Reported High K Materials                                                                                                                                                                                              | 5  |

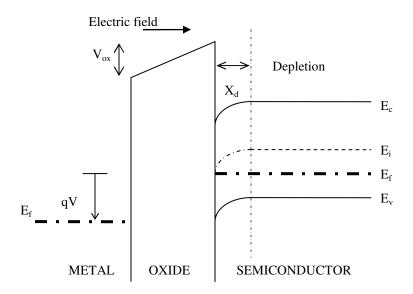

| Figure 2.1  | Band Diagram for Ideal MOS Diode                                                                                                                                                                                       | 9  |

| Figure 2.2  | Band Diagram of MOS at Negative Voltage ( $V_{GS} < 0$ )<br>(Hole Accumulation of the Semiconductor Surface)                                                                                                           | 9  |

| Figure 2.3  | Band Diagram of MOS at Positive Voltage ( $V_{GS} > 0$ )<br>(Hole Depletion of the Semiconductor Surface)                                                                                                              | 10 |

| Figure 2.4  | Band Diagram of MOS at a Large Positive Voltage<br>(Hole Depletion of the Semiconductor Surface)                                                                                                                       | 11 |

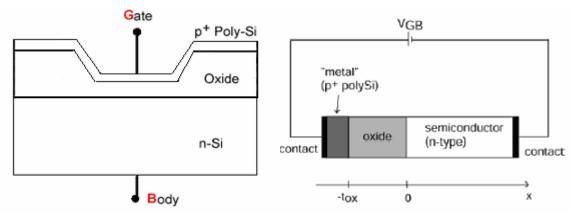

| Figure 2.5  | The MOS Capacitor Structure                                                                                                                                                                                            | 14 |

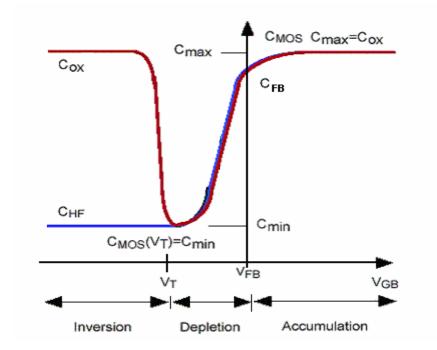

| Figure 2.6  | C-V Characterization of an Ideal MOS Capacitor Structure (n type substrate)                                                                                                                                            | 14 |

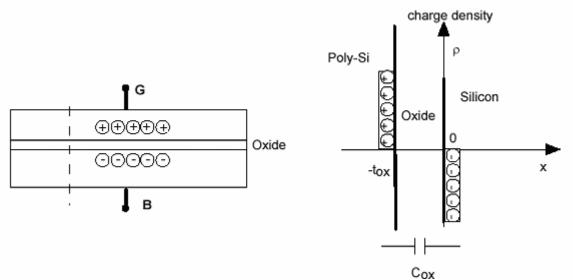

| Figure 2.7  | Charge Distribution in a MOS Capacitor Biased into Accumulation                                                                                                                                                        | 15 |

| Figure 2.8  | Charge Distribution in a MOS Capacitor Biased into Depletion and Equivalent Circuit Diagram                                                                                                                            | 16 |

| Figure 2.9  | Charge Distribution in a MOS Capacitor Biased into Inversion                                                                                                                                                           | 18 |

| Figure 2.10 | <ul><li>(a) A Plot of the High Frequency Capacitance-Voltage of a MOS Capacitor with Different Values of Fixed Oxide Charge.</li><li>(b) The Effect of the Interface States is to "Smear" our the C-V Curves</li></ul> | 20 |

| Figure 2.11 | Cross-Section and Circuit Symbol of an n-channel (MOSFET)                                                                                                                                                              | 22 |

| Figure 2.12 | Top View of MOSFET                                                                                                                                                                                                     | 23 |

| Figure 2.13 | Current-Voltage Characteristics of a MOSFET                                                                                                                                                                            | 26 |

| Figure 2.14 | Basic Structure of a Typical FG Device                                                                     | 28 |

|-------------|------------------------------------------------------------------------------------------------------------|----|

| Figure 2.15 | Flash Cell During a Write Operation                                                                        | 29 |

| Figure 2.16 | Erase Operation Employing Fowler Nordheim Tunneling                                                        | 30 |

| Figure 2.17 | Past Trends in Scaling                                                                                     | 32 |

| Figure 3.1  | Thermionic Emission                                                                                        | 36 |

| Figure 3.2  | Energy Band Diagram for an n+poly-Si/SiO <sub>2</sub> /n-Si Structure in case of Fowler Nordheim Tunneling | 37 |

| Figure 3.3  | Energy Band Diagram for a p+poly-Si/SiO <sub>2</sub> /p-Si Structure in case of Fowler Nordheim Tunneling  | 37 |

| Figure 3.4  | Energy Band Diagram for an n+poly-Si/SiO <sub>2</sub> /n-Si Structure in case of Direct Tunneling          | 38 |

| Figure 3.5  | Triangular Potential Barrier                                                                               | 39 |

| Figure 3.6  | Outline of the Mechanism of Defect Generation Leading to Breakdown of $SiO_2$                              | 44 |

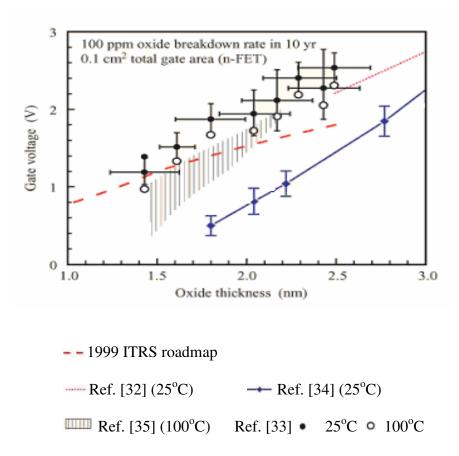

| Figure 3.7  | Oxide Reliability Projections by Different Labs                                                            | 49 |

| Figure 4.1  | I-V Measurement Set up                                                                                     | 55 |

| Figure 4.2  | C-V Measurement Setup                                                                                      | 56 |

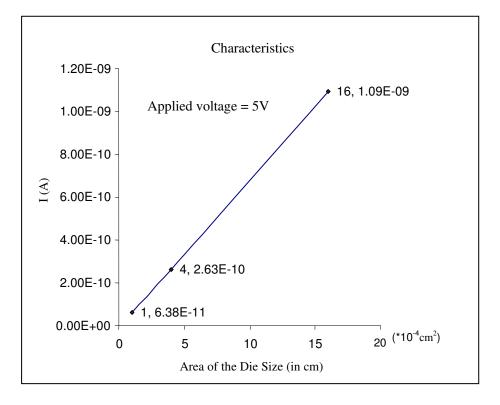

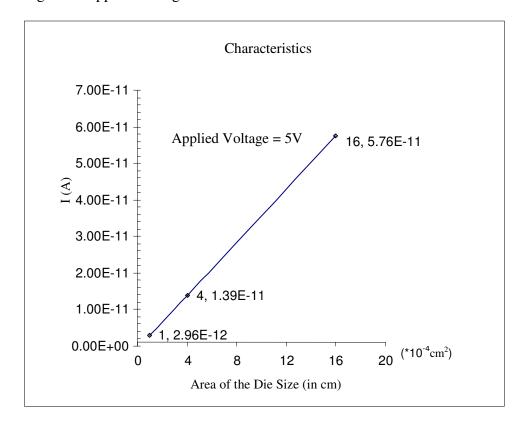

| Figure 4.3  | Plot of Current versus Area for a 7nm n-type Device                                                        | 57 |

| Figure 4.4  | Plot of Current versus Area for a 7nm p-type Device                                                        | 58 |

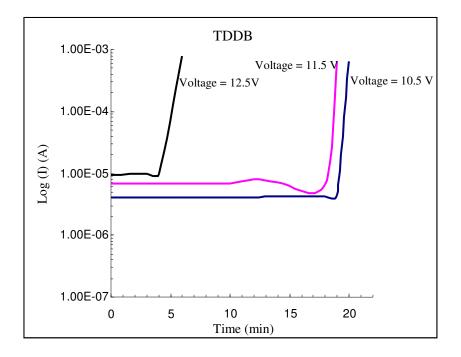

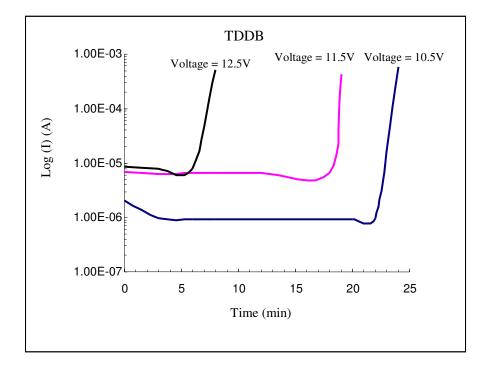

| Figure 4.5  | Time Dependent Dielectric Breakdown Behavior of a 7 <i>nm</i> Oxide Thickness n-type Device                | 60 |

| Figure 4.6  | Time Dependent Dielectric Breakdown Behavior of a 7 <i>nm</i> Oxide Thickness p-type Device                | 60 |

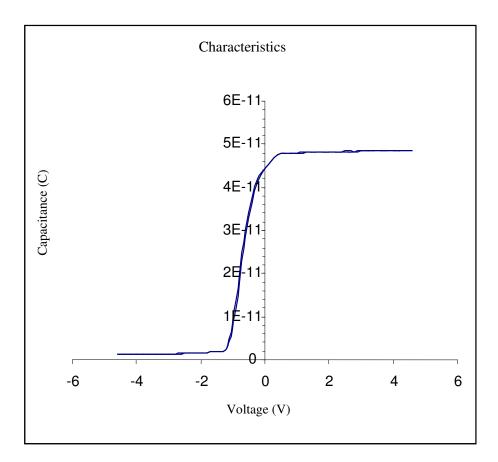

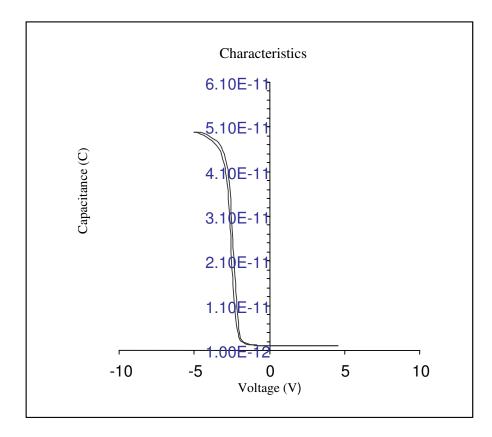

| Figure 4.7  | C-V Characteristics of a 7 nm n-type Device                                                                | 62 |

| Figure 4.8  | C-V Characteristics of a 7 nm p-type Device                                                                | 63 |

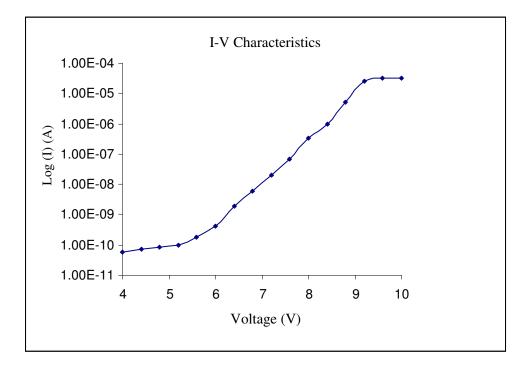

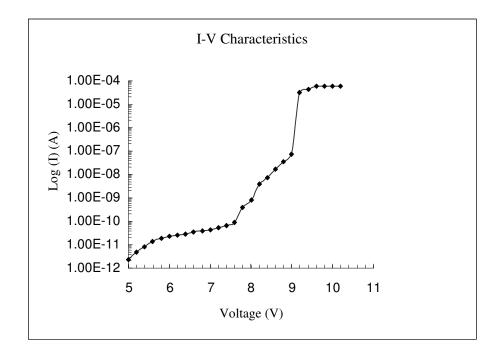

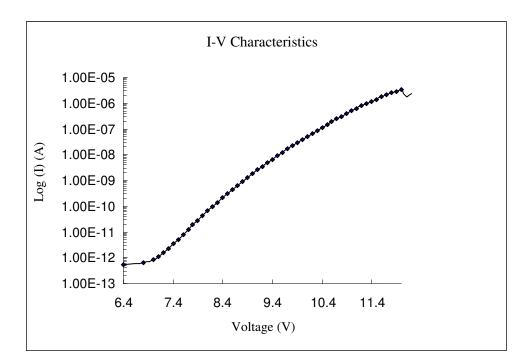

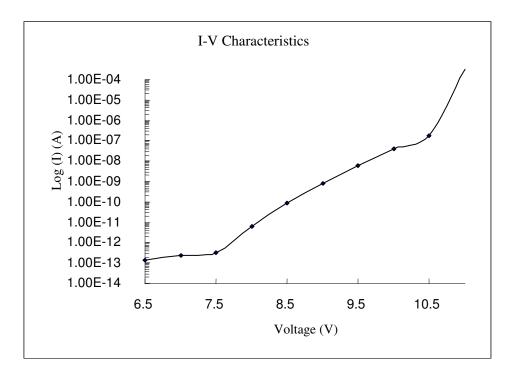

| Figure 4.9  | I-V Characteristic for a 7 nm n-type Device  | 65 |

|-------------|----------------------------------------------|----|

| Figure 4.10 | I-V Characteristic for a 7 nm p-type Device  | 66 |

| Figure 4.11 | I-V Characteristic for a 13 nm n-type Device | 66 |

| Figure 4.12 | I-V Characteristic for a 10 nm p-type Device | 67 |

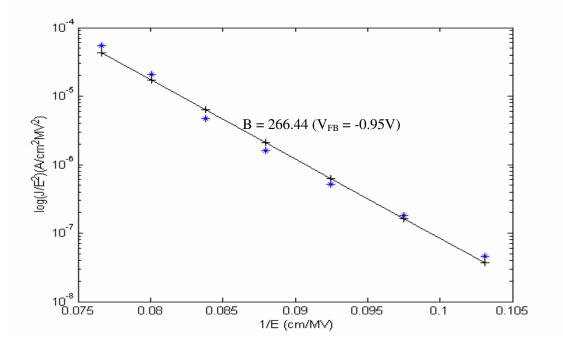

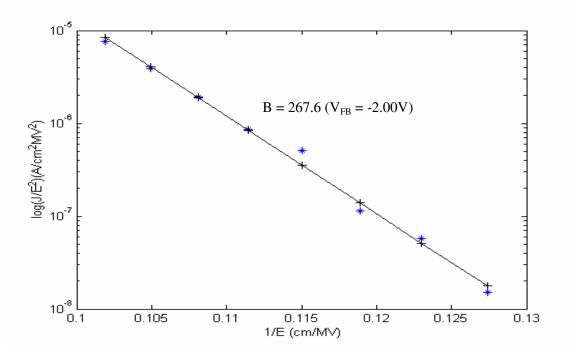

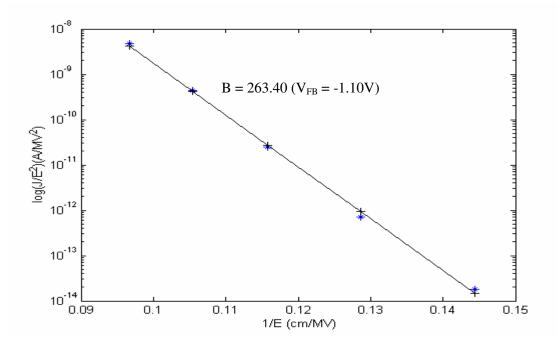

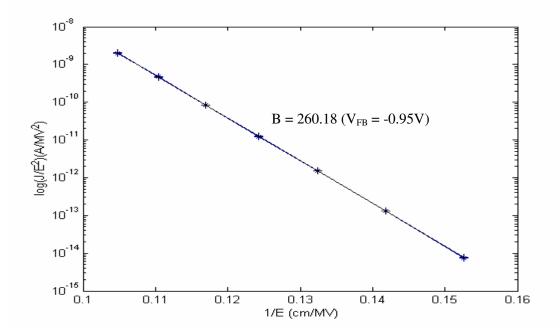

| Figure 4.13 | Fowler-Nordheim Plot for 7nm n-type Device   | 68 |

| Figure 4.14 | Fowler-Nordheim Plot for 7nm p-type Device   | 69 |

| Figure 4.15 | Fowler-Nordheim Plot for 13nm n-type Device  | 70 |

| Figure 4.16 | Fowler-Nordheim Plot for 10nm p-type Device  | 70 |

| Figure B.1  | Front Panel of VI                            | 86 |

| Figure B.2  | Frame 0 of the Block Diagram                 | 87 |

| Figure B.3  | Frame 1 of the Block Diagram                 | 88 |

| Figure B.4  | Frame 3 of the Block Diagram                 | 89 |

#### Investigation of Oxide Thickness Dependence of Fowler-Nordheim Parameter B

Shashank Bharadwaj

#### ABSTRACT

During recent years the thickness of the gate oxide has been reduced considerably. The progressive miniaturization of devices has caused several phenomena to emerge such as quasi-breakdown, direct tunneling and stress induced leakage currents. Such phenomena significantly modify the performance of the scaled-down MOSFETs. As a part of this research work, an effort has been made to study the performance and characteristics of the thin Gate oxide for MOSFETs and Tunnel Oxide for Floating Gate (FG) MOS devices. The exponential dependence of tunnel current on the oxide-electric field causes some critical problems in process control. A very good process control is therefore required. This can be achieved by finding out the exact value of F-N tunneling parameter. This research work also is an effort of finding an accurate value for parameter B and its dependence on the oxide thickness as the device are scaled down to a level where the probability of Direct Tunneling mechanism gains more prominence.

A fully automated Low Current Measurement workstation with noise tolerance as low as  $10^{-15}$  A was set up as a part of this research. C-V and I-V curves were analyzed to extract, determine and investigate the oxide thickness dependence of F-N parameter B. For oxide thickness in the range10~13 *nm*, the parameter B ranged between 260 and 267. Thus it can be said that it is not sensitive to the change in oxide thickness in this range. However it was noticed that for thickness around 7*nm* wide variety of results were obtained for the Fowler-Nordheim parameter B (B ranged from 260 to 454). This can be attributed to the

enhancement in the leakage current due to the direct tunneling. Hence to have tight control over  $V_T$  for a NVM, new algorithms need to be developed for even better process control for oxide thickness in the range of 7 *nm* and below.

#### Chapter 1

#### Introduction

Over the past two decades, the steady downscaling of transistor dimensions has been the main stimulus to the growth of silicon integrated circuits (ICs) and the information industry [1,2]. The more an IC is scaled, the higher becomes its packing density, the higher its circuit speed, and the lower its power dissipation [3]. These have been key in the evolutionary progress leading to today's computers and communication systems that offer superior performance, dramatically reduced cost per function, and much-reduced physical size compared to their predecessors.

The prevailing VLSI technology today comprises CMOS devices because of their unique characteristic of negligible standby power, which allows the integration of tens of millions of transistors on a processor chip with only a very small fraction (<1%) of them switching at any given instant. Also it wouldn't be wrong to state that the microelectronics industry owes a great deal of its success to the existence of the thermal oxide of silicon, i.e., silicon dioxide (SiO<sub>2</sub>). A thin layer of SiO<sub>2</sub> forms the insulating layer between the control gate and the conducting channel of the transistors used in most modern integrated circuits. As circuits are made denser, all of the dimensions of the transistors are reduced ("scaled") correspondingly. As the CMOS dimension, in particular

the channel length, is scaled to the nanometer regime (<100 nm), however, the electrical barriers in the device begin to lose their insulating properties because of thermal injection and quantum-mechanical tunneling [4]. This results in a rapid rise of the standby power of the chip, placing a limit on the integration level as well as on the switching speed. Also the gate oxide has been scaled to a thickness of only a few atomic layers, where tunneling gives rise to a sharp increase in gate leakage currents.

Therefore to sustain the performance trends of last twenty years new solutions such as high dielectric constant and shallow ultra low resistivity junctions need to be developed.

#### **1.1 Gate Dielectrics**

Silicon dioxide has served for more than three decades as the gate insulator responsible for blocking current in insulated gate field-effect transistor channels from the gate electrode in CMOS devices. The reason for the nearly exclusive use of silicon dioxide in this application is that silicon dioxide uniquely possesses the required combination of several properties: good mobility of holes and electrons flowing in silicon at the silicon dioxide interface, ability to keep electronic states (surface states) at this interface low, relatively low trapping rates of holes and electrons, and excellent compatibility with CMOS processing. Since the gate insulator also serves to couple the electric potential from the gate electrode to the channel, the best control of the channel by the gate is obtained when the gate insulator is made as thin as possible

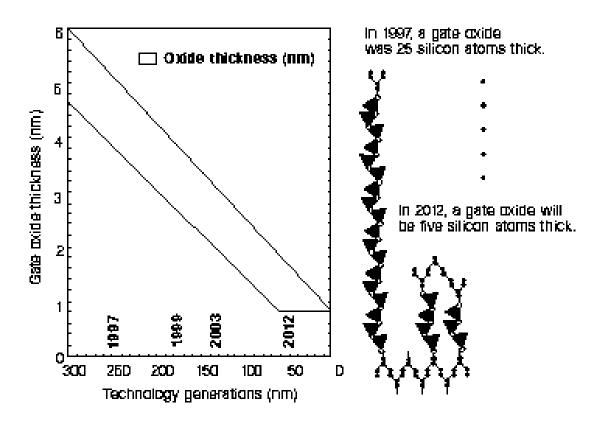

Figure 1.1 Predictions for the Next Few Generations of Chips

Figure 1.1 shows the 1997 prediction for the next few generations of chips [5]. In this plot the generations are defined by a critical device size, which is projected to decrease from 200 nm to 50 nm over the next 12 years. The gate oxide must be reduced in turn, from 25 silicon atoms today to 5 atoms in 2012 to achieve the roadmap goal. Clearly, there must be a limit to this scaling down because the gate-oxide thickness will eventually reach zero. As a matter of fact fundamental limits have been reached for SiO<sub>2</sub> scaling. Increased problems with dopant penetration through ultra thin SiO<sub>2</sub> layers and direct tunneling for ultra-thin oxide films dictate an aggressive exploration for new materials to be used in future gate dielectric applications.

#### **1.2 High K Dielectric**

One possible solution is to use an insulating film with a dielectric constant higher than that for SiO<sub>2</sub>. A high dielectric constant allows the use of a thicker insulating layer for the gate electrode. There are a wide variety of films with higher k values than SiO<sub>2</sub>, ranging from  $Si_3N_4$  with a k value of 7, up to Pb-La-Ti (PLT) with a k value of 1,400. Unfortunately many of these films are not thermodynamically stable on silicon, or are lacking in other properties such as a high breakdown voltage, low defect density, good adhesion, thermal stability, low deposition temperature, ability to be patterned easily and low charge states on silicon. Currently interest seems to be centered on films such as HfO<sub>2</sub> and ZrO<sub>2</sub> with k values of 30-40 and 25 respectively, enabling a 6.4x to 10.3x increase in film thickness for equivalent performance. Intel recently reported over five orders of magnitude reduction of leakage for high-k oxides based on  $HfO_2$  and  $ZrO_2$ versus SiO<sub>2</sub> for equivalent oxide thicknesses. Transistors based on these films showed excellent overall performance. Another film which has shown excellent dielectric property has been  $La_2O_3$  [6]. Although study initiated has been pretty recent,  $La_2O_3$  could well be a good replacement candidate.

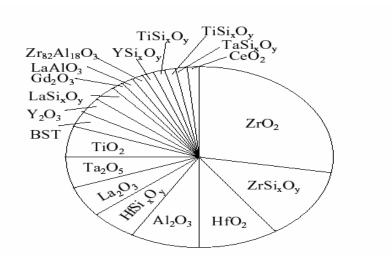

Figure 1.2 gives a brief idea about the effort, research and publications put on the different alternate high-k materials in the last two years or so. It is clearly seen that  $HfO_2$  and  $ZrO_2$  have been most popular research materials as a possible replacement for SiO<sub>2</sub>.

Figure 1.2 Reported High K Materials [7, 8]

#### 1.3 Future Trends in Silicon Technology and Purpose of the Thesis

The guiding principle for the development of high-performance, deep sub-half-micron and sub-quarter- micron, ULSI devices is to increase functions that can be handled in a unit area of the device. Additionally, device reliability must be maintained while enhancing speed performance. During the last decade device physicists, researchers and engineers have been continuously faced with new elements that made the task of MOSFET characterization more and more crucial as well as difficult. The progressive miniaturization of devices has caused several phenomena to emerge such as quasibreakdown, direct tunneling and stress induced leakage currents. Such phenomena significantly modify the performance of the scaled-down MOSFETs. Therefore, the first effort in this research is to study the performance and characteristics of thin Gate oxide MOSFETs. The growing demand of high-density NVM (Non Volatile Memory) for the portable computing and telecommunications market has encouraged serious interest in Flash memory with the capability of multilevel storage and low voltage operation [9]. Multilevel storage implies the capability of storing two bits in a single cell. To do so, four different threshold voltages need to be correctly identified in the FG (Floating Gate) transistor. Even if a single bit is stored in a cell, threshold voltage levels need to be accurately determined to prevent errors from creeping during the write and erase operating modes of flash device. This can be achieved by finding out the exact value of F-N tunneling parameter B.

Research work in this direction has been an ongoing process and a wide range of values for parameter B has been published. However, up to the present time, there are no generally accepted values for parameter B. This research work is an effort of finding an accurate value for parameter B and its dependence on the oxide thickness as the device are scaled down to a level where the probability of Direct Tunneling mechanism gains more prominence. Such studies are necessary in order to obtain a better understanding of the dynamics of the writing and erasing in the memory devices, and the leakage current in the gate for MOSFETS.

Including this Introduction, this thesis contains 5 chapters. In chapter 2, the basic structures and operations of MOS devices have been discussed. Importance of scaling is also presented. Chapter 3 deals with the characterization theory and reliability issues. In chapter 4 analysis has been performed and results justifying the research have been

presented. Chapter 5 discusses the conclusions derived and also presents future work in this direction.

#### Chapter 2

#### **MOS Devices**

#### 2.1 Ideal MOS Diode

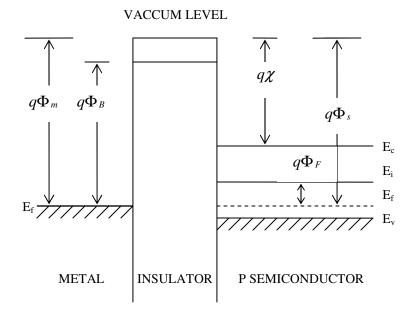

An ideal MOS diode is defined as follows:

1 The energy difference between the metal work function  $\Phi_m$  and the semiconductor work function  $\Phi_s$  is zero.

2 The only charges that can exist in the structure under any biasing conditions are those in the semiconductor and those with the equal but with opposite sign on the metal surface adjacent to the insulator. This is equivalent to oxide charge being zero.

3 The resistivity of the insulator (oxide) is infinite so that there is no carrier transport under dc-bias.

The band diagram for metal, oxide and semiconductor when they are in contact and under zero bias is shown in Figure 2.1. As can be seen at zero applied voltage there is no energy difference between the metal work function  $\Phi_m$  and the semiconductor work function  $\Phi_s$ . In other words the band is flat (flat-band condition) when the applied voltage is zero.

If  $\Phi ms$  is the work function difference then

$$\Phi_{ms} = \Phi_m - \Phi_s = \Phi_m - [\chi + (E_c - E_i)/q + \Phi_F] = 0$$

(2.1)

for p type, where  $\chi$  is semiconductor electron affinity,  $E_c$  the band gap and  $\Phi_F$  the potential difference between the Fermi level and intrinsic Fermi level.

Figure 2.1 Band Diagram for Ideal MOS Diode [10, 11]

**Figure 2.2** Band Diagram of MOS at Negative Voltage ( $V_{GS} < 0$ )

(Hole Accumulation of the Semiconductor Surface)

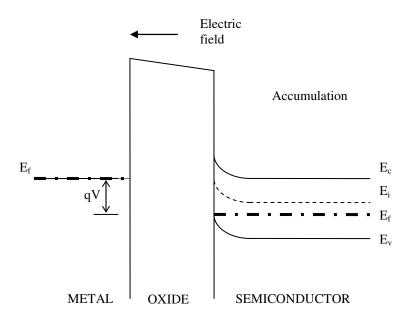

When an ideal MOS diode is biased with positive or negative voltages, three cases may exist at the semiconductor surface. Consider p-type semiconductor as shown in Figure 2.2. Now when a negative voltage V is applied to the metal plate, the top of the valence band bends upward and is closer to the Fermi level. Since the carrier density depends on the energy difference ( $E_F - E_V$ ) and Fermi level remains constant because of no current flow in an ideal MOS, this band bending causes accumulation of majority carriers (holes for p-type and electrons for n-type) near the semiconductor surface. This phenomenon is termed as Accumulation process.

**Figure 2.3** Band Diagram of MOS at Positive Voltage ( $V_{GS} > 0$ )

(Hole Depletion of the Semiconductor Surface)

For  $V_{GS} > 0$  (positive voltage across the metal plate), metal Fermi level is lowered by qV relative to its equilibrium position. As a result, the oxide conduction band is again tilted (moving the metal oxide down relative to the semiconductor side). The positive voltage deposits positive charge on the metal and calls for a corresponding net negative charge at

the surface of the semiconductor. Such a negative charge in the P- type material arises from the depletion of holes from the near surface, leaving behind uncompensated ionized acceptors. This is the depletion case as shown in Figure 2.3. If the voltage is further increased in the positive direction, holes are repelled to a large extent. The bands bend even more downward such that the intrinsic level  $E_i$  at the surface crosses over the Fermi level as seen in Figure 2.4. At this point electrons become the majority carriers. The surface is thus "inverted" and this process is termed as inversion.

Figure 2.4 Band Diagram of MOS at a Large Positive Voltage

(Hole Depletion of the Semiconductor Surface)

It is should be noted that similar results can be obtained for the n-type semiconductor with the polarity of the applied voltage being reversed.

#### 2.1.1 Threshold Voltage

The *threshold voltage* of an MOS transistor is the voltage required to turn on the transistor and allow current flow between the drain and source nodes. The transistor is considered to be turned on when an *inversion layer* has been established in the channel. An inversion layer is said to be established when the electrostatic potential between the bulk semiconductor and the oxide-semiconductor surface (called surface potential,  $\Phi_S$ ) is twice the Fermi potential  $\Phi_F$ . For an nMOS transistor, when  $\Phi_S = 2\Phi_F$ , the p-type substrate semiconductor acts like an n-type semiconductor at the surface, and thus the transistor is in inversion.

The fundamental equation for MOS threshold voltage,  $V_T$  is

$$V_T = 2\Phi_F - \frac{Q_B}{C_{OX}} \tag{2.2}$$

To understand this equation better, certain parameters need to be defined at this stage. The Fermi potential  $\phi_{F}$  is the difference (in volts) between the intrinsic energy level and the Fermi energy level deep inside the semiconductor substrate (i.e. away from the oxide surface).

$$\phi_F = \frac{E_i - E_F}{q} \tag{2.3}$$

$$E_i - E_F = kT \ln\left(\frac{N_A}{n_i}\right)$$

(2.4)

and

where  $N_A$  is the substrate impurity concentration. Hence the Fermi potential for an nMOS transistor can be written as:

$$\phi_F = \frac{kT}{q} \ln \left( \frac{N_A}{n_i} \right) \tag{2.5}$$

When a transistor is in inversion, there is a depletion layer in the device channel (under the gate oxide) which provides a charge that must be balanced by the gate voltage. Thus, the threshold voltage must also account for this depletion charge. This charge in the bulk depletion layer, which is due to ionized impurities, is given by:

$$Q_B = -qN_A X_d = -\sqrt{2q\varepsilon_s N_A(2\phi_F)}$$

(2.6)

where  $X_d$  is the depletion layer width and is given by

$$X_d = \left[\frac{2\varepsilon_s \phi_s}{qN_A}\right]^{1/2} \tag{2.7}$$

#### 2.1.2 MOS Capacitor under Bias

MOS capacitor consists of a metal-oxide-semiconductor layer structure which forms a voltage dependent capacitor. The most common MOS capacitor structure is shown in Figure 2.5. As seen the metal plate is a heavily doped  $p^+$  poly-silicon layer. The insulating layer is silicon dioxide and the other plate of the capacitor is the semiconductor layer (in this case its an n-type silicon).

The capacitance depends on the voltage applied to the gate with respect to the body (substrate) and the frequency. This dependence is shown in Figure 2.6 (high as well as low frequency). There are roughly three regions of operation separated by two voltages. These are (1) *Accumulation* in which carriers of the same type as the body accumulates at the surface (2) *Depletion* in which the surface is devoid of any carriers leaving only a

space charge or depletion layer, and (3) *Inversion* in which carriers of the opposite type from the body aggregate at the surface to "invert" the conductivity type.

Figure 2.5 The MOS Capacitor Structure [12]

Figure 2.6 C-V Characteristics of an Ideal MOS Capacitor (n type substrate) [12]

The two voltages that demarcate the three regimes are *Flatband Voltage* ( $V_{FB}$ ) which separates the accumulation regime from the depletion regimes and the *Threshold Voltage*.

#### 2.1.2.1 Surface Accumulation

$V_{FB}$  is the voltage at which there is no charge on the plates of the capacitor and hence there is no electric field across the oxide. Hence it's also called Flatband voltage and is zero for ideal MOS diode. Now when  $V_{GB}$  (applied voltage) >  $V_{FB}$  a positive charge is induced on the "metal" gate and a corresponding negative charge in the semiconductor. For an n-type silicon electrons accumulate at the surface. This condition is termed as surface accumulation. The charge distribution and equivalent circuit is shown in Figure 2.7. In accumulation the MOS structure appears like a parallel-plate capacitor and the MOS capacitance per unit area is given by

$$C = C_{OX} = \mathcal{E}_{OX} / t_{OX}$$

(2.8)

Where  $\varepsilon_{OX}$  is the permittivity of the oxide and  $t_{OX}$  is the thickness of the oxide.

Figure 2.7 Charge Distribution in a MOS Capacitor Biased into Accumulation [12]

#### 2.1.2.2 Surface Depletion ( $V_T < V_{GB} < V_{FB}$ )

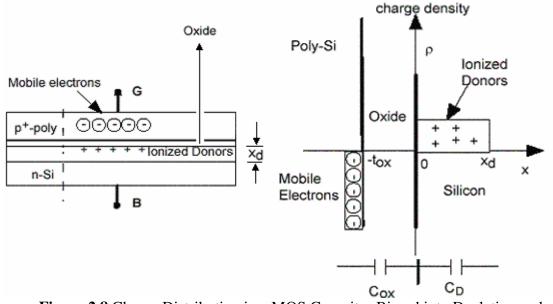

If the applied voltage is less then the Flatband voltage, a negative charge is induced at the interface between the poly-silicon gate and the gate oxide. This leads to a positive charge being induced at the other interface i.e. the oxide/semiconductor interface. As a result the surface of the semiconductor is devoid of any mobile carriers (this being a n-type substrate). This layer at the surface is termed as the depletion layer as it prevents carriers from moving towards the semiconductor-oxide interface. Charge distribution under these circumstances is as shown in Figure 2.8. As seen this layer can be said to behave as an capacitor having a capacitance per unit area ( $C_D$ ), which depends on  $V_{GB}$  and is given by

$$C_D = \varepsilon_{Si} / X_d$$

(2.9)

Where  $\varepsilon_{si}$  is the permittivity of the silicon and  $X_d$  is the depleted silicon layer thickness. It

should be noted from the equation that  $C_D$  and  $X_d$  are function of the input voltage.

Figure 2.8 Charge Distribution in a MOS Capacitor Biased into Depletion and

Equivalent Circuit Diagram [12]

A closer look at the figure will lead to another conclusion that oxide capacitance per unit area ( $C_{OX}$ ) and the depleted silicon capacitance per unit area ( $C_D$ ) are connected in series. Thus the capacitance of the MOS structure in the depletion regime is given by:

$$1/C_{MOS}(dep) = 1/C_D + 1/C_{OX} = (C_{OX} + C_D)/C_D * C_{OX}$$

(2.10)

#### 2.1.2.3 Surface Inversion ( $V_T > V_{GB}$ )

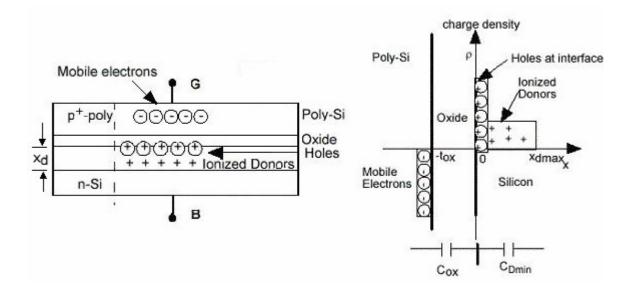

Now consider a scenario where the applied gate voltage is lowered below the threshold voltage. The number of electrons decreases as the applied voltage decreases. Correspondingly the number of holes increases. This is owing to the fact that in a MOS capacitor in depletion or inversion, the holes and electrons are generated in the depleted silicon surface region. The holes are attracted to the Si/SiO<sub>2</sub> interface while the electrons are "pushed" into the substrate. However the holes could also come from a p-doped region that is in close proximity to the MOS capacitor such as the source/drain region of a n-MOSFET. Thus at a voltage less then the threshold voltage, V<sub>T</sub>, the concentration of the holes at the surface far exceeds the concentration of electrons in the bulk. The conductivity type of the silicon surface is inverted. Figure 2.9 shows the charge distribution of the MOS capacitor in inversion.

**Figure 2.9** Charge Distribution in a MOS Capacitor Biased into Inversion [12] After surface inversion, the depletion layer thickness reaches a maximum. Thus when the gate voltage is equal to the threshold voltage, the depleted layer capacitance per unit area reaches a minimum  $C_{Dmin}$  and likewise the MOS capacitance. This capacitance is given by

$$C_{\min}(inv) = C_{OX}C_{D\min} / C_{D\min} + C_{OX}$$

(2.11)

#### 2.1.3 Non Ideal MOS Capacitor

The work function of the gate material  $\Phi_m$  is not necessarily same as the work function of the semiconductor, and as a result there is a built-in potential across the gate oxide. This built-in potential is equal to the work function difference  $\Phi_{ms.}$  A voltage applied to the gate must account for this work function difference before an inversion layer can be established. Thus, for a non ideal MOS Capacitor, threshold voltage, as defined by equation 2.2 changes to

$$V_t = \phi_{MS} + 2\Phi_F - \frac{Q_B}{C_{OX}} - \frac{Q_{OX}}{C_{OX}}$$

(2.12)

where  $Q_{ox}$  is the oxide charge and is explained in detail below.

The discussion about the ideal MOS capacitor assumed that there were no oxide charges in the oxide region. In a practical MOS capacitor, interface traps and oxide charges exist and affect the ideal MOS characteristics. These charges have energy states in the forbidden silicon band gap region and are able to exchange charges with the silicon in a short time. The interface trap charge  $Q_{it}$  charges can possibly be produced by excess silicon, excess oxygen, and impurities. The fixed oxide charges  $Q_f$  are located at or near the interface and are immobile under an applied electric field. The oxide trapped charges  $Q_{ot}$  can be created by hot-electron injection. These charges are distributed inside the oxide layer. The mobile ionic charges  $Q_m$  such as sodium ions, are mobile within the oxide under bias-temperature aging conditions.

The presence of oxide charge causes a voltage drop across the oxide, which is given by

$$\Delta V = \frac{-Q_{ss}}{C_{ox}} \tag{2.13}$$

In equation 2.12  $Q_{ss}$  is the total oxide charge. The entire C-V curve shifts to a more negative value if  $Q_{ss}$  is positive.

**Figure 2.10** (a) A Plot of the High Frequency Capacitance-Voltage of a MOS Capacitor with Different Values of Fixed Oxide Charge. (b) The Effect of the Interface States is to "Smear" out the C-V Curves

A typical shift in the C-V characteristic is depicted in Figure 2.10a. The value of  $Q_{ss}$  can be obtained by measuring the shift with respect to the calculated ideal curve. Such measurements are very important for characterizing the quality of MOS devices. The

shift in the C-V curve is due to the fact that  $Q_m$ ,  $Q_f$  and  $Q_{ot}$  are constant and independent of voltage.

The interface charge has a somewhat different effect on the C-V characteristics. In an ideal system, there are no electron states allowed in the bandgap of a semiconductor. However, since the  $Si - SiO_2$  interface is not ideal, a certain density of interface states are produced that lie in the bandgap region. In contrast to the fixed charge, the electrons can flow into and out of these interface states. However, the electron motion is dependent upon the position of the fermi level. The nature of the interface states is characterized as either "acceptor-like" or "donor-like". An acceptor state is neutral if it is unoccupied, which occurs if the fermi level is below the state. An acceptor state is negatively charged if it is occupied, which occurs if the fermi level is above the state. A donor state is neutral if it is occupied, which occurs if the fermi level is above the state. A donor state becomes positively charged if it is unoccupied, which occurs if the fermi level is below the state. As a result, when the position of the fermi level is altered, the charge at the interface changes and the voltage drops. When the interface charge is positive the C-V curve shifts towards the negative voltage. When the interface charge is negative the curve shifts towards the positive voltages. The amount of shift is voltage dependent and is depicted schematically in Figure 2.10b. The curve is "smeared out" due to the presence of interface states.

#### **2.2 MOSFET**

#### 2.2.1 Basic Structure and Principle of Operation of the MOSFET

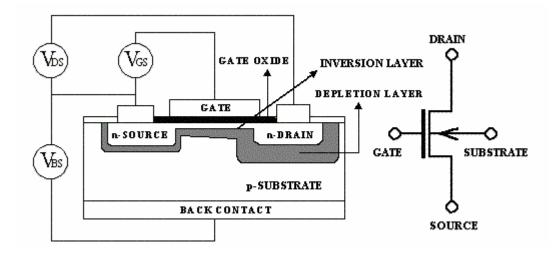

A Metal-Oxide-Semiconductor Field-Effect-Transistor (MOSFET) is a four terminal device. The n-channel version of the device and the corresponding circuit symbol are illustrated in Figure 2.11. As shown it consists of a source and a drain, two highly conducting n-type semiconductor regions which are isolated from the p-type substrate by reversed-biased p-n diodes. A metal (or poly-crystalline) gate covers the region between source and drain, but is separated from the semiconductor by the gate oxide.

Figure 2.11 Cross-Section and Circuit Symbol of an n-channel (MOSFET)

As can be seen, the source and drain regions are identical when no voltage is applied. It is the applied voltages, which determine which n-type region provides the electrons and becomes the source, while the other n-type region collects the electrons and becomes the drain. The voltages applied to the drain and gate electrode as well as to the substrate by means of a back contact are referred to the source potential. A conceptually similar structure was first proposed and patented by Lilienfeld and Heil [13] in 1930. The main technological problem was the control and reduction of the surface states at the interface between the oxide and the semiconductor.

Initially it was only possible to deplete an existing n-type channel by applying a negative voltage to the gate. Such devices have a conducting channel between source and drain even when no gate voltage is applied and are called "depletion-mode" devices. In contrast there are other set of devices, which do not have a conducting channel unless a positive voltage is applied. Such devices are referred to as "enhancement-mode" devices. The electrons at the oxide-semiconductor interface are concentrated in a thin (~10 nm thick) "inversion" layer. By now, most MOSFETs are "enhancement-mode" devices.

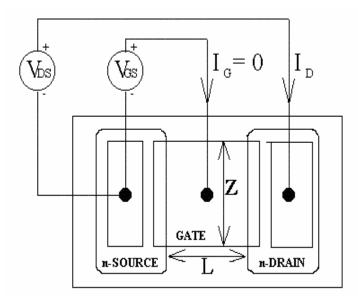

Figure 2.12 Top View of MOSFET

A top view of the same MOSFET is shown in Figure 2.12, where the gate length, L, and gate width, Z, are identified. Note that the gate length does not equal the physical dimension of the gate, but rather the distance between the source and drain regions

underneath the gate. The overlap between the gate and the source/drain region is required to ensure that the inversion layer forms a continuous conducting path between the source and drain region. Typically this overlap is made as small as possible in order to minimize its parasitic capacitance. The flow of electrons from the source to the drain is controlled by the voltage applied to the gate. A positive voltage applied to the gate attracts electrons to the interface between the gate dielectric and the semiconductor. These electrons form a conducting channel between the source and the drain called the inversion layer. No gate current is required to maintain the inversion layer at the interface since the gate oxide blocks any carrier flow. The net result is that the current between drain and source is controlled by the voltage, which is applied to the gate.

#### 2.2.2 Current-Voltage Characteristics of the MOSFET

The electrical function of a MOSFET is to carry current between its source and drain terminal depending on the applied gate voltage. Any proper analysis of the MOSFET requires that charge flow in the device be studied in three dimensions. Several models have been proposed to find the characteristics of the device. The simplest model is discussed here. This model assumes that the mobility of the electron is constant and independent of the electric field. This is a good assumption for the long channel MOSFET. The condition for the n-MOSFET to be in the cut off region, where the current is zero, is when  $V_G - V_S < V_T$ . When the MOSFET is in the cut off region the source and drain are electrically isolated with respect to one another. When on, a bias is applied between the source and the drain, current flows in the channel near the Si-SiO<sub>2</sub> interface. The charge density in the channel is controlled by the gate bias as well as the source-drain bias. Therefore, the gate bias can modulate the current flow in the channel. In order to find the current in the device, a constant electron mobility has been assumed. The current is assumed to be due to carrier drift and is given by

$$I_D = Q_n \mu_n \frac{dV_s}{dx} Z \tag{2.14}$$

where  $Q_n$  is the charge due to electrons within the inversion layer and is the difference between the total surface charge  $Q_s$  and  $Q_B$  after strong inversion.

The current,  $I_D$  is assumed constant throughout the cross-section of the channel. Thus

$$I_D dx = Q_n \mu_n Z dV_s \tag{2.15}$$

The integration of equation 2.14 throughout the length of the device gives

$$I_{D} = \frac{\mu_{n} Z C_{ox}}{L} \left[ \left\{ V_{GS} - V_{T} - \frac{V_{DS}}{2} \right\} \right] V_{DS}$$

(2.16)

Equation (14) is valid for the device before pinch off. In the case when the drain bias,  $V_{DS}$  is much less than  $V_{GS} - V_T$ , the current equation is given by

$$I_{D} = \frac{\mu_{n} Z C_{ox}}{L} \left[ (V_{GS} - V_{T}) V_{DS} \right]$$

(2.17)

For very small values of drain bias, the current increases linearly with drain bias because of the  $\frac{\mu_n ZC_{ox}}{L}$  factor in equation 2.17. Therefore, it is defined as the linear region.

As the drain voltage is increased, the voltage across the oxide decreases near the drain, which forces  $Q_n$  to decrease. As a result, the channel becomes pinched off at the drain end and the current saturates. The saturation condition is given approximately by

$$V_{DS}(sat) = V_{GS} - V_T \tag{2.18}$$

and

$$I_D(sat) = \frac{\mu_n Z C_{ox}}{2L} \left[ (V_{GS} - V_T)^2 \right] \quad . \tag{2.19}$$

The drain current at saturation remains essentially constant for larger values of drain voltage.

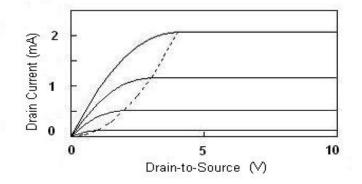

Figure 2.13 Current-Voltage Characteristics of a MOSFET

Figure 2.13 depicts the typical I-V characteristics of a MOSFET [14]. The dotted line separates the two main regions of operation, which are the linear and saturation regions.

#### 2.2.3 Importance of MOSFET

One of the major advantages of this type of FET in semiconductor industry is that it amplifies electrical signals. The current gain is made possible owing to the fact that no gate current is required to maintain inversion layer. The device therefore has an infinite current gain in DC. The voltage gain of the MOSFET is caused by the fact that the current saturates at higher drain-source voltages, so that a small drain current variation can cause a large drain voltage variation. In addition MOSFET devices exhibit excellent switching characteristics owing to different region of operations. MOSFET can also be used as a resistor. Resistor characteristics are obtained by permanently biasing the gate terminal for conduction. The ratio of the source-drain voltage to the channel current then determines the value of resistance. A particularly useful device for digital applications is a combination of n-channel and p-channel MOS transistors on adjacent regions of the chip. Such a semiconductor device is termed as Complementary MOS (or CMOS). The basic circuit is an inverter. The beauty of this circuit is that one of the devices is turned in either condition (input 1 or input 0). As a result CMOS structures greatly reduces power consumption. Hence it has found wide spread acceptance in the design of high density complex digital circuits.

#### 2.3 Non Volatile Memory (NVM)

Nonvolatile Memory is a device into which the data can be programmed electrically and which will retain data even in the absence of a power supply. The basic operating principle of the nonvolatile memory devices is the storage of charge in the gate insulator of a MOSFET. This has led to the subdivision of devices into two groups namely the MIOS (Metal Insulator Oxide Semiconductor) and the FGMOS (Floating Gate Metal Oxide Semiconductor). This research work concentrates on FGMOS which is most commonly used as compared to MIOS in flash memories.

The FGMOSFET is the basic building block of the flash memory cell [9, 15]. In this device the charges are injected from the silicon across the first insulator and stored in the insulator-oxide interface of the floating gate of the FGMOS. Fowler Nordheim tunneling techniques can be used to write as well as erase data.

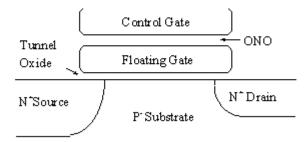

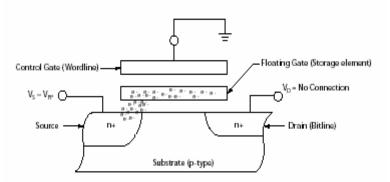

# 2.3.1 Structure of a Typical Floating Gate Device

The schematic cross section of an FG device is presented in Figure 2.14. The top electrode, also known as the control gate (word line), has a provision for direct electrical access. Below the control gate is the floating gate, which is capacitively coupled to the control gate and the underlying silicon. Generally, the floating gate is separated from the

Figure 2.14 Basic Structure of a Typical FG Device

control gate by a stacked Oxide-Nitride-Oxide(ONO) dielectric. Electrical access to the floating gate is only through capacitors.

### **2.3.2 Operation Conditions**

Table 1 summarizes the bias conditions, which identify the three operational modes of an Industry Standard cell. The Program (Write) and Erase and Read operation modes are discussed in the following chapters.

|         | SOURCE          | DRAIN           | CONTROL GATE    |  |  |

|---------|-----------------|-----------------|-----------------|--|--|

| PROGRAM | GND             | V <sub>dd</sub> | V <sub>pp</sub> |  |  |

| ERASE   | V <sub>cc</sub> | Float           | GND             |  |  |

| READ    | READ GND        |                 | V <sub>cc</sub> |  |  |

**Table 2.1** Source, Drain and Control Gate Biases for Operation of a Typical Flash Call

# 2.3.2.1 Write Operation

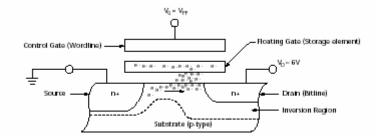

Flash and EPROM implement hot electron injection to place charge on the floating gate during a WRITE. Figure 2.15 shows the cell bias condition during Program operation During a WRITE, a high programming voltage  $(V_{pp})$  is placed on the control gate. This

Figure 2.15 Flash Cell During a Write Operation [16]

forces an inversion region to form in the p-type substrate. The drain voltage is increased to approximately half the control gate voltage while the source is grounded (0 volts), increasing the voltage drop between the drain and source as shown in Figure 2.15. With the inversion region formed, the current between drain and source increases. The resulting high electron flow from source to drain increases the kinetic energy of the electrons. This causes the electrons to gain enough energy to overcome the oxide barrier and collect on the floating gate. After the WRITE is completed, the negative charge on the floating gate raises the cell's threshold voltage ( $V_T$ ) above the wordline logic 1 voltage. When a written cell's wordline is brought to logic 1 during a READ, the cell will not turn on. The sense amps detect and amplify the cell current and output a "0" for a written cell.

# **2.3.2.2 Erase Operation**

Flash employs Fowler-Nordheim tunneling to remove charge from the floating gate to bring it to the erased state. Using high-voltage source erase, the source is brought to a high voltage (VPP), the control gate grounded (0 volts) and the drain left unconnected as shown in Figure 2.16. The large positive voltage on the source, as compared to the floating gate, attracts the negatively charged electrons from the floating gate to the source through the thin oxide. Because the drain is not connected, the ERASE function is a much lower current-per-cell operation than a WRITE that uses hot electron injection. After the ERASE is completed, the lack of charge on the floating gate lowers the cell's VT below the wordline logic 1 voltage. When an erased cell's wordline is brought to a logic 1 during a READ, the transistor will turn on and conduct more current than a written cell.

Figure 2.16 Erase Operation Employing Fowler Nordheim Tunneling [16]

Some flash devices use Fowler-Nordheim tunneling for WRITEs as well as ERASEs.

#### 2.4 MOS Device Scaling

Early transistors were crude by today's standards, having channel lengths of greater then 10um, gate oxide thickness greater then 100 *nm* and operating at 12 V. As a result integrated circuits in those times had around 10000 MOS transistors only and operated at frequencies less then 1 MHz. Today, however, MOS transistors have channel lengths less then 0.1um, gate oxide thickness less then 10 nm and operate at 3.3V. Integrated circuits today use more then 3 million transistors and the operating frequency is more then 100 MHz. Table 1 shows the past trends in transistor scaling [17]:

Table 2.2 Historical Trends in Scaling

|                     | 1977 | 1980 | 1983 | 1986 | 1989 | 1992 |

|---------------------|------|------|------|------|------|------|

| Gate Length (um)    | 3    | 2    | 1.5  | 1.1  | 0.7  | 0.6  |

| Channel length (um) | 2    | 1.5  | 1.2  | 0.9  | 0.6  | 0.4  |

| Gate Oxide (nm)     | 70   | 40   | 25   | 25   | 20   | 15   |

| Junction Depth (um) | 0.6  | 0.4  | 0.3  | 0.25 | 0.20 | 0.15 |

| Gate Delay (ps)     | 800  | 350  | 250  | 200  | 160  | 90   |

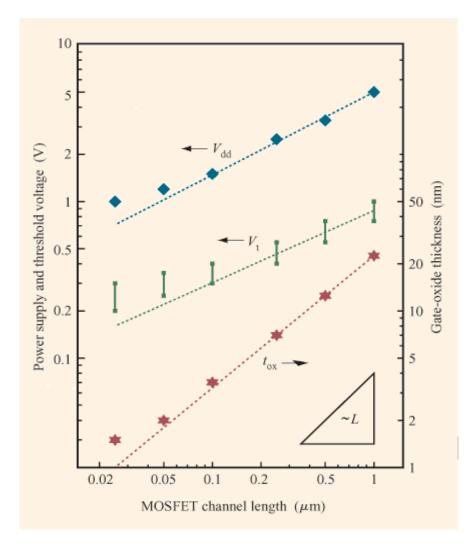

MOS technology dimensions are being aggressively scaled to such a plateau where device performance must be accessed against fundamental limits. The exponential growth in the last three decades has been largely driven by technological innovations and have enabled a steady reduction in MOSFET dimensions. However, moving further, scaling will not be as rampant as it has been in the past. This is owing to the fact that when the dimensions of a MOSFET are scaled down, both the voltage level and the gate-oxide thickness must also be reduced. Figure 2.17 shows the scaling trend of power-supply voltage ( $V_{dd}$ ), threshold voltage ( $V_T$ ), and gate-oxide thickness ( $t_{ex}$ ) as a function of CMOS channel length [2]. As seen that the power-supply voltage has not been decreasing at a

rate proportional to the channel length. This means that the field has been gradually rising over the generations between 1- $\mu$ m and 0.1- $\mu$ m channel lengths. The effect of this increase in electric field is not felt because thinner oxides are still reliable at such high electric field, thus allowing operation at the reduced but nonscaled supply voltages

Figure 2.17 Past Trends in Scaling [2]

Therefore it can be said that a point will be reached in the near future at which further gains from scaling of traditional planar CMOS devices will be very difficult, limited by

leakage due to direct tunneling and switching power considerations. Further expansion in the specialization of device structures and design points will proceed over the next few generations of CMOS, with increased emphasis on new materials and structures. As of now the Tunnel oxide in NVM has been scaled down to 8 *nm*.

# Chapter 3

# **Characterization of Thin Gate Oxide**

# **3.1 Introduction**

The microelectronics industry owes a great deal of its success to the existence of the thermal oxide of silicon, i.e., silicon dioxide (SiO<sub>2</sub>). A thin layer of SiO<sub>2</sub> forms the insulating layer between the control gate and the conducting channel of the transistors used in most modern integrated circuits. Although no insulator is ideal, amorphous SiO<sub>2</sub>, with a bulk resistivity of ~10<sup>15</sup> th-cm and dielectric breakdown strength of ~10<sup>7</sup> V/cm, is one of the best nature has provided [3]. Its usefulness in silicon technology is due to the fact that films of this material can be grown by thermal oxidation of clean silicon surfaces, and that the resulting films can be made with sufficiently low densities of charge traps. In addition, the energy barrier (conduction-band discontinuity) between Si and SiO<sub>2</sub> is 3.1 eV, only about 1 eV lower than the Si/vacuum barrier. Silicon dioxide uniquely possesses the required combination of several properties: good mobility of holes and electrons flowing in silicon at the silicon dioxide interface, ability to keep electronic states (surface states) at this interface low and excellent compatibility with CMOS processing.

Continuous device scaling requires the continued reduction of the gate dielectric thickness. This needs to be done to keep short-channel effects under control. Therefore

gate oxide thickness is reduced almost in the same proportion as the channel length. This is necessary in order for the gate to retain more control over the channel than the drain. For CMOS devices with channel lengths of 100 nm or less, an oxide thickness less then 3 *nm* is needed [18]. This thickness comprises only a few layers of atoms. Oxide film this small no longer acts as a perfect barrier. A leakage current, dependent on the applied voltage and the corresponding electric field, exists. This phenomenon can be attributed to the Quantum-mechanical tunneling [19]. As the silicon dioxide scaling reaches its fundamental limits, direct tunneling effects are more felt now then ever before.

# **3.2 Current Conduction Mechanism**

The lifetime of a particular gate oxide thickness is determined by the total amount of charge that flows through the gate oxide by leakage current. Ideally, an oxide doesn't allow charge to pass through. However this is not the case when the electric fields become high and the oxide becomes thin. There are several mechanisms that allow charge to pass through the oxide. For oxide layers thicker than 6 nm, the leakage current mechanism is explained by Fowler-Nordheim electron tunneling in MOS structures [20]. On the other hand, the tunneling in the ultra-thin oxide layers (2-5nm), as already examined by Maserjian in 1974 [21], has been termed as direct tunneling.

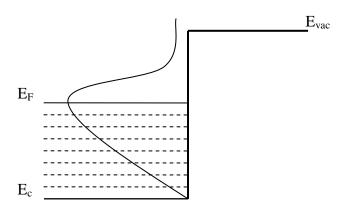

### 3.2.1 Thermionic Emission

Figure 3.1 Thermionic Emission

In a conducting material, the electrons are governed by Fermi-Dirac statistics. The baseline electron energy is the Fermi Energy, and at low temperatures the electrons all exist at or below this level. As temperature is increased, so the distribution function for the electrons develops a high energy 'tail'. Some of these electrons have sufficient energy to pass over the surface potential barrier between the material and the vacuum. This process of increasing the temperature of a bulk material to increase the number of electrons which can leave the material is called thermionic emission. The thermionic emission has also been observed in metal-oxide structures.

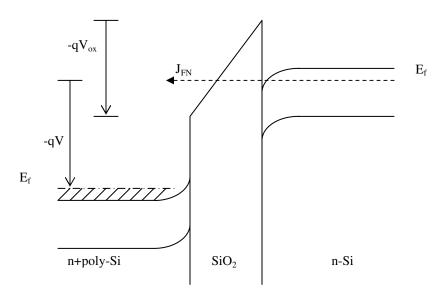

# **3.2.2 Fowler-Nordheim Tunneling**

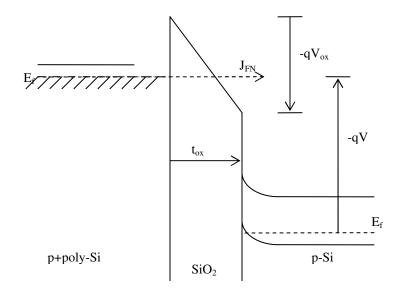

Fowler Nordheim tunneling is a quantum mechanical tunneling process where the electrons can penetrate through the oxide barrier into the conduction band of the oxide (Figure 3.2). Fowler-Nordheim tunneling is dependent on the voltage across the gate

oxide and increases exponentially with the applied voltage. It can occur in most any gate oxide, provided the voltage is sufficient for electrons to tunnel through the barrier. Figure 3.3 shows the F-N tunneling mechanism for a p+poly-Si/SiO<sub>2</sub>/p-Si structure.

Figure 3.2 Energy Band Diagram for an n+poly-Si/SiO<sub>2</sub>/n-Si Structure in Case of Fowler

# Nordheim Tunneling

Figure 3.3 Energy Band Diagram for a p+poly-Si/SiO<sub>2</sub>/p-Si Structure in Case of Fowler

Nordheim Tunneling 37

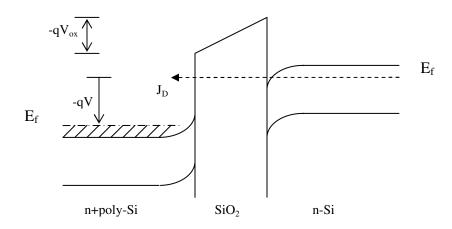

# **3.2.3 Direct Tunneling**

Direct tunneling is also a quantum mechanical tunneling process as shown in Figure 3.4. Direct tunneling is a phenomenon that is important to understand in ultrathin oxides. It occurs when electrons tunnel through the gate oxide region directly from the gate to the channel region and vice versa. Direct tunneling is dependent on the thickness of the gate region; it increases exponentially as the thickness of the oxide decreases. Direct tunneling is relatively independent of the electric field across the gate oxide.

Figure 3.4 Energy Band Diagram for an n+poly-Si/SiO<sub>2</sub>/n-Si Structure in Case of Direct Tunneling

The difference between Fowler-Nordheim tunneling (FNT) and direct tunneling (DT) of electrons is determined by the shape of the tunnel barrier. If the oxide tunnel barrier is triangular, FNT occurs while DT takes place through trapezoidal barrier. The transition from FNT to DT occurs if the difference in potential energy over the oxide layer qVox becomes smaller than the barrier height at the injecting interface.

# **3.2.4** Analytical Expressions for the Tunnel Currents

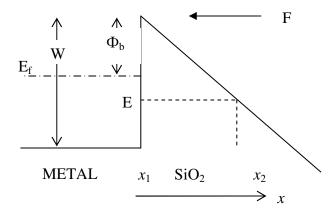

For a simplified metal-semiconductor or heterojunction or a band to band transition can be approximated by a triangular potential barrier. For a triangular potential barrier as shown Figure 3.5 the tunneling probability  $T_t$  can be given by WKB approximation (Wentzel-Kramer-Brillouim method) as shown below:

$$T_t = \exp\left[-2\int_{x_1}^{x_2} |k(x)| dx\right]$$

(3.1)

where |k(x)| is the absolute value of the wave vector of the carrier in the barrier, and  $x_1$ and  $x_2$  are the classical turning points as shown in the figure below:

Figure 3.5 Triangular Potential Barrier

The value of k can be found from the conservation of energy and momentum which is justified only in the tunneling process and is given by

$$\frac{h^2 k^2}{2m} = [U - E]$$

(3.2)

where E is the electron energy and U the potential energy and is given by

$$U = W - qFX \quad \text{for } x > 0 \tag{3.3}$$

where F is the electric field. Replacing this value of U in equation 3.2 gives the value for k. By substituting this value of k in equation 3.1 tunneling probability can be rewritten as

$$T_{t} = \exp\left[-\frac{4}{3}\left(\frac{2m}{h^{2}}\right)^{1/2}\frac{(W-E)^{3/2}}{F}\right]$$

(3.4)

The tunneling current density  $J_{FN}$  in a three dimensional lattice from the n type Si accumulation layer to poly-Si gate or from the gate electrode to the accumulation layer of p-Si can be obtained from the equation below

$$J = q \iiint \frac{2}{h^3} T_t V_x dP_x dP_y dP_z$$

(3.5)

where  $V_x$  is the velocity due to electrons in the x direction.

Replacing the tunneling probability  $T_t$  as described in equation 3.4 in 3.5 it can be shown that

$$J_{FN} = AF^2 \exp\left[-\frac{B}{F}\right]$$

(3.6)

where,

$$A = \frac{q^3}{16\pi^2 h \phi_b} \text{ and } B = \frac{4}{3} \frac{(2m_{ox})^{1/2}}{qh} \phi_b^{3/2}$$

These are two basic parameters for the gate oxide tunnel current calculation and the parameters A and B depend on the tunnel barrier height  $\Phi_b$  and the effective mass of the tunneling electron  $m_{ox}$  and can be derived from a F-N plot of  $\ln(J_{FN} / F^*F)$  vs. 1/F. The slope of this straight line gives B while A is determined from the intercept.

It is clear from these relationships that operating a CMOS device at voltages greater than foundry specification results in an exponential increase in the amount of oxide current. Once electrons have breached the oxide potential barrier they are accelerated through the oxide by the electric field which is determined by the applied voltage and the oxide thickness. Charge accelerated in the gate oxide achieves greatest energy at the oxidesilicon interface presuming there have been no collisions in transit. At the end of its travel through the oxide, it deposits its energy at the oxide-silicon interface.

Making these equations as the basis of the analytical part of this research work, results are presented in the following chapter.

In the case of direct tunneling the current density, where the potential barrier takes a rectangular shape, is given by [22]

$$J_{D} = \frac{AF^{2}}{\left[1 - \left(\frac{\phi_{s} - qV_{ox}}{\phi_{s}}\right)^{1/2}\right]^{2}} \exp\left[-\frac{B}{F} \frac{\phi_{s}^{3/2} - (\phi_{s} - qV_{ox})^{3/2}}{\phi_{s}^{3/2}}\right] * \left\{1 - \exp\left[-\frac{3}{2} \frac{\phi_{s}^{1/2} - (\phi_{s} - V_{ox})^{1/2}}{\phi_{s}^{3/2}}E_{f}\right]\right\}$$

$$(3.7)$$

#### **3.3 Dielectric Breakdown**

The reliability of  $SiO_2$  in microelectronics, i.e., the ability of a thin film of this material to retain its insulating properties while subjected to high electric fields for many years, has always been a concern and has been the subject of numerous publications over the last 35–40 years, ever since the realization that  $SiO_2$  could be used as an insulating and passivating layer in silicon-based transistors [23, 24]. The gate leakage current causes

increased power consumption and may affect device and circuit functionality. Thus, the leakage current imposes a practical limit on oxide thickness. The current flowing through an ultrathin gate oxide is not merely a nuisance parasitic, but also causes reliability problems by leading to long-term parameter shifts (wear out) and eventually to oxide breakdown

### **3.3.1 Time Dependent Dielectric Breakdown (TDDB)**

The time dependent nature of the breakdown, or TDDB, is one of the most heavily researched failure mechanisms in the semiconductor reliability community. Since the 1960s, researchers have struggled to understand the nature of how an oxide degrades over time [25]. By definition, TDDB is wear-out of the insulating properties of silicon dioxide in the CMOS gate leading to the formation of a conducting path through the oxide to the substrate. With a conducting path between the gate and the substrate, it is no longer possible to control current flow between the drain and source by means of the gate electric field. TDDB lifetime is strongly affected by the number of defects in the gate oxide produced during wafer fabrication. Therefore, foundries strive to produce an ultraclean oxide in their process to maximize the TDDB lifetime. Even if a foundry could produce a perfectly defect free oxide, TDDB would remain a concern for ASIC (Application Specific Integrated Circuit) designers. TDDB occurs at all gate voltage bias conditions. The goal of the foundry is to trade off gate oxide thickness with operating voltage specifications to achieve both speed and lifetime targets for the technology. The

lifetime of a particular gate oxide thickness is determined by the total amount of charge that flows through the gate oxide by leakage current.

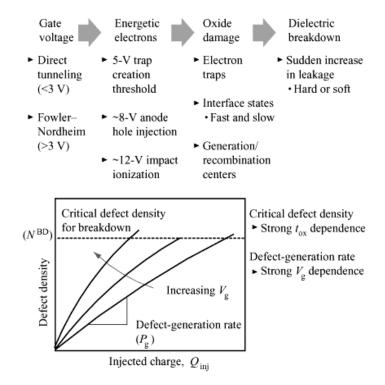

# 3.3.2 Dielectric Breakdown Models

The essential elements of our present understanding of oxide wear out and breakdown are illustrated in Figure 3.6. The figure represents outline of the mechanism of defect generation leading to breakdown in  $SiO_2$ . The gate voltage causes energetic electrons to flow across the oxide, leading to a buildup of damage in the form of microscopic defects which act as electron traps. When sufficient defect density is reached, the oxide no longer acts as a good insulator.

Electrons flowing across the oxide trigger several processes depending on their energy, which is determined by the gate voltage for thin oxides. At least three defect-generation mechanisms have been identified: impact ionization, anode hole injection and trap creation process attributed to hydrogen release from the anode. These models form the basis of the different analysis and tests Reliability engineers perform to check device performance.

Figure 3.6 Outline of the Mechanism of Defect Generation Leading to Breakdown of SiO<sub>2</sub> [26]

### 3.3.2.1 Bandgap Ionization Models

DiMaria (IBM Microelectronics) developed the Bandgap Ionization in the early 1990s [27]. He postulated that when the energy of an electron approaches the energy of a bandgap (~ 9eV), electron-hole pairs can be generated that cause defects in the oxide. This process occurs in dielectrics thicker than ~ 20nm at fields higher than ~ 7 MV/cm, and is associated with the high-energy tails of the electron distribution. Although this model was popular in the early to mid 1990s, it is not in wide use today. Soon afterward, researchers began reporting data on ultra thin oxides that could not be reconciled with the

Bandgap Ionization model. While the model is valid for thicker oxides, it is not as valid for ultra thin oxides.

#### 3.3.2.2 Anode Hole Injection Model

Schuegraf and Hu developed the Classic Anode Hole Injection Model in the mid 1990s [28]. The Classic Anode Hole Injection Model, commonly called the 1/E model, was the source of some controversy in the late 1990s as researchers sided either it or with the Thermo chemical (E) model. Schuegraf and Hu postulated that a fraction of the electrons entering the anode have enough energy to create a "hot" hole which can tunnel back into the oxide. These holes then in turn create defects in the oxide. Their equation modeling the process predicts a 1/E dependency, hence the name 1/E (see equation below).

Some researchers have suggested based on both theoretical and experimental evidence that significant injection and trapping of anode holes does not occur until the electron obtains a sufficiently high energy (~7.6 eV) in the anode. Recent studies using improved models for impact ionization suggest that anode hole injection can occur at low energies and that the dependence of anode hole induced breakdown on voltage is linear. However, there are no known studies conclusively showing that anode injected holes at low voltage are trapped in the oxide and lead to breakdown.

### 3.3.2.3 Hydrogen Release Model

Di Maria and his colleagues developed The Hydrogen Release Model after physically observing the behavior and properties of the oxides during and after stress [29]. DiMaria (and others) observed hydrogen release and buildup after stressing various oxide structures. He postulated that energetic electrons create oxide damage by interacting with the oxide lattice itself or with a secondary species such as hydrogen. Based on data taken at IBM he determined that hydrogen release requires electrons with energy levels of at least 5 eV in the anode, and 2 eV in the oxide.

### **3.4 Reliability**

Reliability engineers also study the statistics associated with the oxide breakdown. There have been many models proposed but the most commonly models referred to for analysis are Percolation or Spheres model of breakdown [30] and Weibull distribution [31]. A detailed explanation of these models and reliability projections is beyond the scope of this research work.

Breakdown is generally understood to be the result of a gradual and predictable buildup of defects such as electron traps in the oxide, but the precise point at which breakdown occurs is statistically distributed so that only statistical averages can be predicted. The rate of defect generation in the oxide is proportional to the current density flowing through it, and therefore the reliability margin for gate-oxide breakdown has been drastically reduced as a consequence of device scaling. At present, predicted reliability "limits" for the gate-oxide thickness range from less than 1.5 nm to 2.8 nm. Dielectric breakdown occurs by two mechanisms: extrinsic or intrinsic failure. Extrinsic failures occur with a decreasing failure rate over time and are caused by process defects such as metallic, organic, or other contaminants on the crystalline silicon surface, and by surface roughness. Most extrinsic failures occur early in the lifetime of a device and can cause significant reliability problems as the number of dielectric failures exceed a predefined specification. Failure rates generated extrinsically can be reduced by applying a burn-in or voltage screening process to the devices. The failures are accelerated at elevated voltages and temperatures. These procedures screen out dielectric defects before the product is shipped, thereby containing early life failure rates within product specifications. Minimizing extrinsic defects in a process and reducing dielectric fails early in the life cycle of a product is important for processing ultrathin gate dielectrics. It is also critical that reliability testing detect systematic and/or random types of processinduced defects that may contribute to an increase in number of dielectric failures. In fullscale product manufacturing, in-line monitoring of both yield and reliability ensures the tight process control of defects to minimize the device and/or chip failures. The second type of failure for a thin gate dielectric, sometimes referred to as wear-out, is intrinsic to the material. Intrinsic failures occur with an increasing failure rate over time and are usually caused by an inherent imperfection in the dielectric material. It is essential that these fails do not occur during the intended useful lifetime of the device when it is operating under specified conditions. The intrinsic failure of ultrathin gate dielectric has been the subject of intensive research. The process of intrinsic degradation in gate dielectric begins with trap creation and formation of interface states as the device gate dielectric is stressed at elevated voltages and temperatures. The creation of these defects continues with the injected current (and therefore time) until the defect density reaches a critical value, after which dielectric breakdown occurs. Parameters that affect when and

how the dielectric breakdown occurs include the applied stress voltage, temperature, dielectric thickness, device dielectric area, and intrinsic dielectric lifetime.

### **3.4.1 Reliability Projections**

Figure 3.7 shows various oxide-reliability projections from different research groups . Plotted in this figure is the maximum allowable voltage that can be applied to the total gate area on a chip, such that no more than a specified failure rate will result. The failure rate in this case is defined as the fraction of chips which will experience one or more oxide breakdown events. As can be ascertained from this figure, there remains considerable disagreement among laboratories regarding this reliability limit for SiO<sub>2</sub>. The various projections in this figure are compared to the latest international roadmap for the operating voltage and physical oxide thickness. Note that various laboratories may use different methods to determine the oxide thickness, which can produce results varying by as much as 0.4 nm. As a rule of thumb, a factor of 10 change in any reliability criterion (e.g., lifetime, failure rate, device area) results in ~0.1 nm change in the minimum  $t_{ox}$  for a given supply voltage.

It is clear that there is no agreement at the present time regarding the correct oxidereliability extrapolation. While all of the estimates for the minimum  $t_{ox}$  are rather closely clustered in the 1.5–2.5-nm range, this is precisely the range of interest for the industry roadmap, and it represents a large variation in device performance and circuit density. Thus, the situation is complicated by the fact that neither a worst-case or a best-case outlook can be adopted safely. The worst-case scenario appears to be unacceptable from a

Figure 3.7 Oxide Reliability Projections by Different Labs

technological and economic perspective, and the best-case scenario is risky because even in this case there are no margin for error. Thus, it appears that the traditional method of assessing oxide reliability, by observing the breakdown time during an accelerated stress experiment and extrapolating this to operation conditions using physical or empirical models, may no longer be adequate to convincingly ensure the long-term reliability of products based on CMOS circuits. It has therefore become necessary to look in more detail at the nature of the breakdown event and the behavior of devices and circuits after oxide failure.

# Chapter 4

# **Determination and Extraction of Parameter B**

# 4.1 Introduction

The Fowler Nordheim tunneling-injection mechanism is widely used in NVM, particularly in EEPROM. There are three main reasons for this choice: first, tunneling is a pure electrical mechanism; second, the involved current level is quite low and thus allows the internal generation of supply voltages needed for all operations; third, it allows one to obtain the time to program (1 ms) 12 orders of magnitude shorter than retention time (10 y), which is a fundamental request for all NVM technologies.